DIGITAL

TIME-FREQUENCY-DOMAIN

50

- ELETTRONICA OGGI 452 - MARZO 2016

telecomunicazioni per effettuare la canalizzazione e la ricom-

binazione dei canali di telecomunicazione. In applicazioni di

monitoraggio dello spettro, esse sono usati per determinare

quali frequenze sono presenti all’interno della banda moni-

torata, mentre nel campo dell’elaborazione delle immagini la

DFT e la IDFT sono sfruttate per gestire la convoluzione di im-

magini con una unità di filtraggio per effettuare, ad esempio,

il riconoscimento dell’immagine. Tutte queste applicazioni

sono tipicamente realizzate usando un algoritmo più efficien-

te rispetto a quello qui sopra mostrato per calcolare la DFT.

Come già detto, la capacità di comprendere e di eseguire una

DFT all’interno di un FPGA è una competenza che ogni svi-

luppatore che opera nel settore dovrebbe possedere.

Una soluzione basata su Fpga

L’esecuzione della DFT e della IDFT come qui descritta si pre-

senta sotto la forma di una serie di cicli annidati, ciascuno

dei quali effettua N calcoli. Il tempo richiesto per effettuare i

calcoli della DFT è dato da:

DFTtime = N * N * Kd ft

dove Kdft è il tempo di elaborazione per ciascuna iterazione

che deve essere eseguita. Chiaramente, la sua esecuzione

può diventare molto lunga. Per questo motivo, le DFT all’inter-

no di un FPGA sono normalmente eseguite usando un algo-

ritmo noto come trasformata di Fourier veloce (FFT Fast Fou-

rier Transform). Quest’ultima differisce leggermente dagli

algoritmi DFT a causa del fatto che calcola la DFT complessa

– ossia lavora sui segnali reale e immaginario nel dominio

del tempo e produce risultati nel dominio della frequenza di

ampiezza pari a N bit anziché N/2. Quindi nel momento in cui

si desidera calcolare una DFT reale, è necessario azzerare la

parte immaginaria e portare il segnale nel dominio del tempo

nella parte reale. Per eseguire una FFT all’interno di un FPGA

Xilinx è possibile sfruttare due opzioni: scrivere un algorit-

mo FFT partendo da zero usando un linguaggio HDL oppure

potete usare un blocco IP che esegue una FFT (disponibi-

le all’interno del catalogo IP della Vivado Design Suite o da

terze parti). A meno che non esistano motivi validi per non

ricorrere al blocco IP, solo la riduzione del tempo di sviluppo

ottenuta dall’uso dei core di Xilinx dovrebbe costituire un va-

lido motivo di scelta. L’approccio di base della FFT prevede

la scomposizione del segnale nel dominio del tempo in più

segnali elementari nel dominio del tempo. Questo processo

è spesso chiamato inversione di bit (bot reversal), dato che i

campioni vengono riordinati. Il numero di stadi che occorro-

no per creare questi segnali elementari nel dominio del tem-

po è calcolato come Log2N, dove N è il numero di bit, se non

è usato un algoritmo di inversione dei bit come “scorciatoia”.

Questi segnali elementari nel dominio del tempo vengono

quindi usati per calcolare gli spettri di frequenza per ciascu-

no di questi punti. L’operazione è piuttosto immediata, dato

che lo spettro di frequenze è uguale al dominio del tempo dei

segnali elementari. È nella ricombinazione di questi punti a

singola frequenza che l’algoritmo FFT diventa complicato. È

infatti necessario ricombinare questi spettri uno stadio alla

volta, operazione opposta della scomposizione nel dominio

del tempo. Di conseguenza, occorreranno ancora Log2N sta-

di per ricreare gli spettri: a questo punto entra in scena la

FFT butterfly. Rispetto al tempo di esecuzione della DFT, la

FFT richiede un tempo dato da:

FFTtime = K f ft * N Log2 N

che indica un miglioramento significativo in termini di tempo

di esecuzione richiesto per calcolare la trasformata. Quan-

do si esegue una FFT all’interno di un FPGA è necessario

prendere in considerazione le dimensioni della FFT. Queste

ultime determineranno il rumore di fondo al di sotto del qua-

le non è possibile vedere i segnali di potenziale interesse. Le

dimensioni della FFT determineranno anche la distanza fra i

componenti in frequenza. Per determinare le dimensioni del-

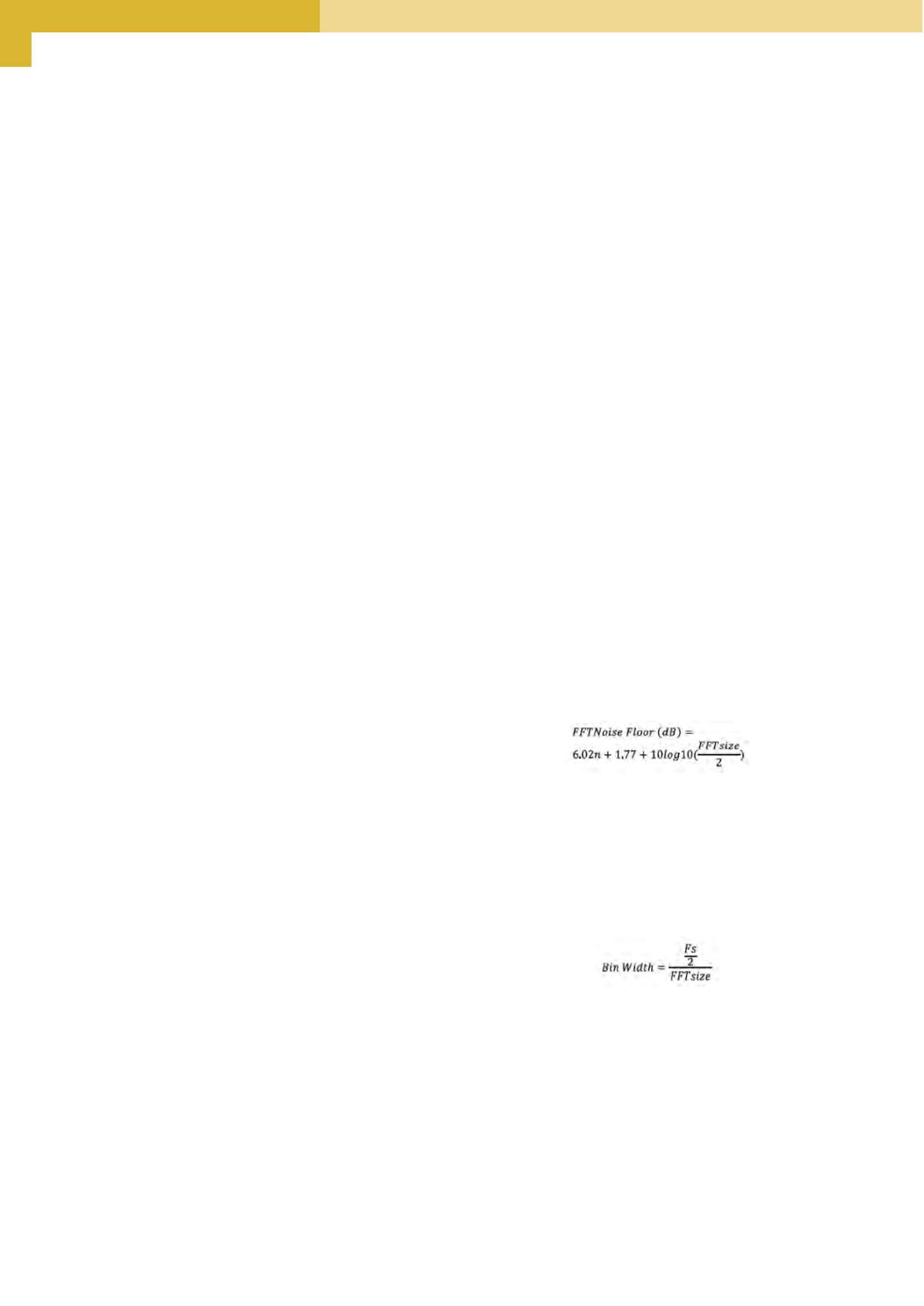

la FFT è necessario usare la seguente equazione:

dove N è il numero di bit quantizzati all’interno del dominio

del tempo e FFTSize rappresenta le dimensioni della FFT. Per

un’esecuzione basata su FPGA, questa è normalmente una

potenza di due – ad esempio, 256, 512, 1.024, ecc. I compo-

nenti in frequenza saranno uniformemente distanziati secon-

do questa formula:

Ad esempio una frequenza di campionamento (FS) di 100

MHz con una dimensione di FFT di 128 avrebbe una risolu-

zione in frequenza di 0,39 Hz. Questo naturalmente significa

che frequenze che cadono all’interno di un intervallo di 0,39

Hz l’una dall’altra non possono essere distinte.

Campionamento ad alta velocità

Molte applicazioni delle FFT all’interno di FPGA e nei sistemi

ad alte prestazioni operano a frequenze molto elevate. Il fun-

zionamento ad alta frequenza può presentare alcune proble-