21

- ELETTRONICA OGGI 451 - GENNAIO/FEBBRAIO 2016

TECH INSIGHT

EMC

semplice: per riduzione di costi si sono ridotti i nanometri dei

canali dei gate, con riduzione dei tempi di attraversamento e

per comodità i fogli tecnici non sono stati modificati perché

contengono non i tempi minimi, ma quelli massimi garantiti.

Un qualunque prodotto consumer da poche decine di euro

contiene DSP, FPGA, ASIC, microcontrollori con tempi di com-

mutazione anche di 100 psec e core di calcolo di 30 psec. Le

bande convenzionali corrispondenti sono di 3 GHz e 10 GHz

rispettivamente.

Il progettista digitale che non ama analogica e RF si trova a

progettare circuiti a microonde, con gli spazi disponibili presso-

ché inesistenti dei multistrati digitali e antenne non intenzionali

sparse ovunque sulla scheda.

La riduzione delle dimensioni degli integrati (i nanometri che da

oltre i 100 di ieri oggi sono scesi ai 50) per varie ragioni, tra

cui quelle di assorbimenti e calore, porta a una velocizzazione

dei segnali di scambio informazioni (da Mbit a Gbit), rendendo

problematico il superamento delle prove. Già oggi in molti casi

per il progettista è più impegnativo superare le prove EMC che

quelle funzionali. E sotto questo profilo le cose sono destinate a

peggiorare.

La riduzione delle dimensioni comporta strati sempre più sottili

e componenti più fragili e più suscettibili ai disturbi che vagano

ovunque con telefonia mobile, WiFi, WiMax.

Le protezioni interne dall’ESD degli integrati si riducono al punto

che basta qualche scarica, anche lontana, per deteriorarle fino

a perdere la funzione protettiva. Si crede di avere un compo-

nente già protetto, mentre sarebbe meglio pensare che la pro-

tezione non ci sia del tutto. Per quanto riguarda le alimentazioni

degli integrati la tendenza ovviamente è quella di usare tensioni

sempre più basse: da 5 VDC a 3,3 VDC, a 1,75 VDC...

Nel prossimo futuro i dispositivi portatili potrebbero essere

alimentati a 1V (molto sotto non si può più andare con il si-

licio), e la distanza tra il livello 1 e il livello 0 – che era nella

tecnologia TTL di 1,5V – sarà di 0,3V. Di quanto aumenta la su-

scettibilità al rumore? È ragionevole ritenere che in un prossi-

mo futuro saranno suscettibili anche i componenti digitali che

oggi sono per lo più immuni. Se oggi è possibile concentrare

l’attenzione nella valutazione della suscettibilità sui soli com-

ponenti analogici a basso livello di segnale, domani lo scena-

rio sarà completamente diverso.

Il punto di svolta

La progettazione elettronica, almeno quella più evoluta, è a

una svolta. Integrati con più di 1.000 contatti, clock sopra 1

GHz, comunicazioni wireless a bordo scheda, modificano

completamente il progetto elettronico, a cominciare dal cir-

cuito stampato.

Se un tempo la preoccupazione era concentrata sui cavi, sulle

masse, sul contenitore, oggi i problemi sono localizzati negli

stampati a molti strati con SMD su due lati e microvia o conte-

nitori che devono schermare nelle bande S e C nonostante le

molte aperture presenti.

Le statistiche dicono che ormai la maggior parte degli stam-

pati nel mondo ha più di 6 strati e che quasi tutti contengo-

no linee a impedenza controllata, in buona parte anche linee

differenziali. In Italia, dove l’elettronica industriale è prepon-

derante rispetto a quella consumer, esistono molti prodotti

che tramite interfacce LVDS “portano a spasso” clock ad alta

frequenza o che contengono antenne per comunicazioni wi-

reless da rendere compatibili con i componenti montati sulle

schede. In sintesi, i problemi EMC tipici dell’elettronica consu-

mer si estendono anche ai prodotti industriali nostrani.

La svolta riguarda anche i metodi di progettazione che non

possono più essere basati sulle formule approssimate usate

ieri, ma su strumenti di simulazione di signal integrity ed EMC

piuttosto raffinati e costosi.

Piste, stack, impedenze, diafonie, jitter, stub, ritardi, adatta-

menti, schermi di bordo, risonanze, decap, emissioni irradia-

te, devono essere calcolati su stampati con più di 1.000 piste.

L’adozione di questi strumenti innovativi richiede addestra-

mento di personale e tempi lunghi. Ma non se ne potrà più

fare a meno, l’alternativa è uscire dal mercato dell’elettronica.

L’uso esteso di questi strumenti ridurrà anche prototipazioni

e sperimentazioni, con un cambiamento radicale del tipo di

compiti assegnati al progettista.

Lo scenario è lo stesso già visto nel campo della simulazione

dinamica real-time, che ha portato con successo all’abbatti-

mento della sperimentazione, all’accorciamento dei tempi di

sviluppo del prodotto e alla contrazione dei costi.

Quello che era un esperimento innovativo è diventato realtà

prima e routine poi.

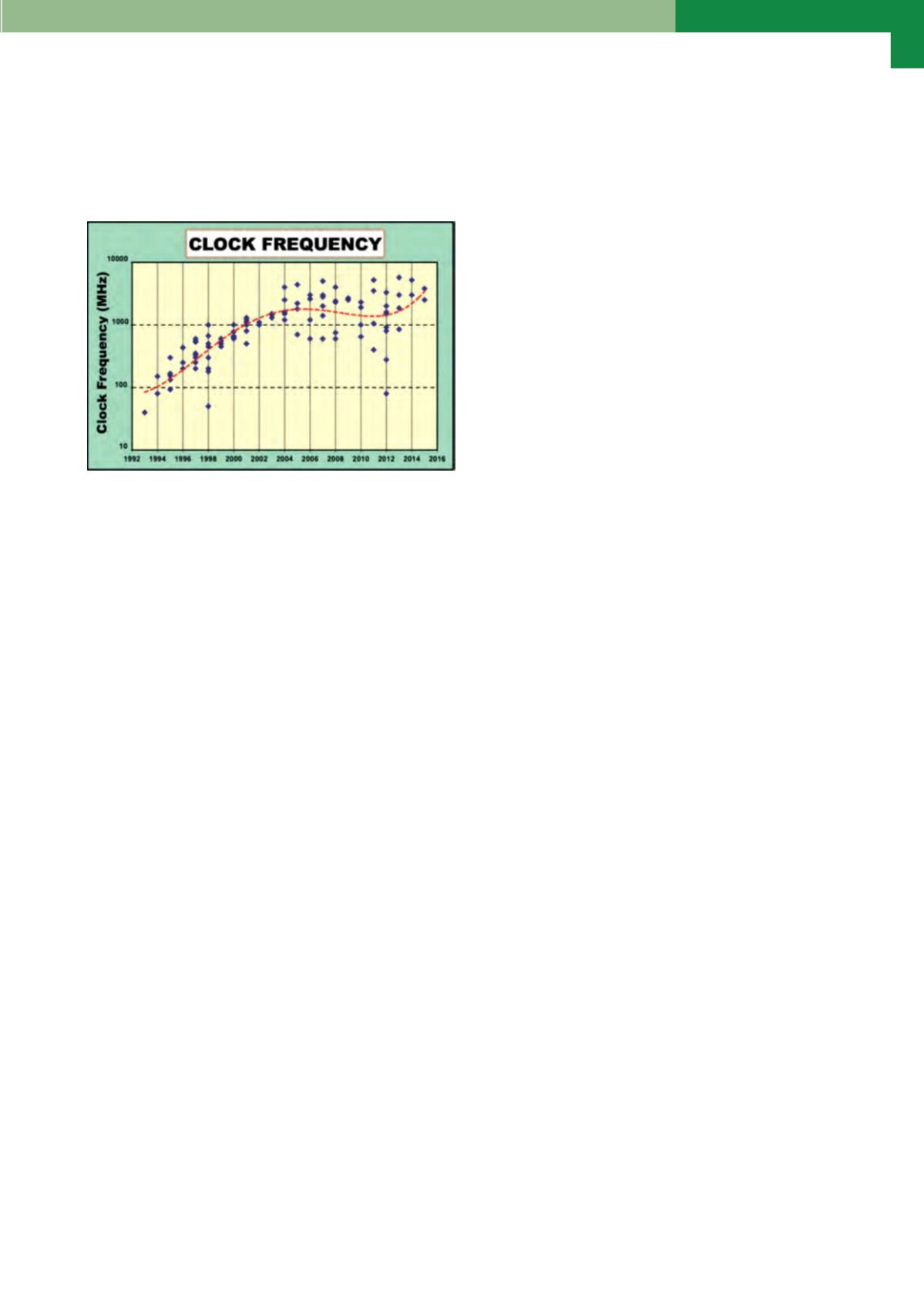

Fig. 2 – La massima frequenza di clock sembra per il momento atte-

starsi a 5-6 GHz, principalmente per motivi termici (Fonte: ISSCC-

International Solid State Circuits Conference, 2015 – San Francisco

– 22-26 febbraio 2015)