DIGITAL

ENERGY HARVESTING

42

- ELETTRONICA OGGI 449 - OTTOBRE 2015

ma sono quelle che avranno il maggior impatto sui consumi

di energia complessivi. Un’operazione cruciale è minimizzare

le attività non necessarie, conseguibile mediante un utilizzo

“intelligente” delle modalità di “sleep”. Ulteriori miglioramenti

possono essere ottenuti scegliendo architetture di processo-

re in grado di ottimizzare la quantità di lavoro svolto durante

ogni ciclo di clock.

I microcontrollori di solito prevedono più di una modalità

di “sleep” a basso consumo: da una più “leggera”, in cui la

memoria locale e la maggior parte delle periferiche restano

alimentate mentre il core della CPU è nello stato di “idle” a

una più “profonda” (deep-sleep mode) dove la maggior parte

delle funzioni sono state disabilitate e non sono alimentate.

Minore è il numero delle periferiche e delle funzioni del core

abilitate, maggiori saranno i risparmi energetici. Ma non bi-

sogna dimenticare i vari compromessi a livello di progetto.

Solitamente, un nodo sensore IoT dovrà effettuare il moni-

toraggio dell’ambiente circostante e reagire nel momento in

cui variano le condizioni del sistema. Al fine di ottimizzare

un sistema embedded a basso consumo, in particolar modo

uno che sfrutta sorgenti intermittenti di alimentazione come

accade se si utilizzano tecniche di energy harvesting, è in-

dispensabile individuare la modalità di “sleep” a più basso

consumo che garantisca una risposta adeguata al verificarsi

eventi in real-time.

La modalità di “sleep” a più basso consumo di un microcon-

trollore integrato in un sistema reale è quello in cui un RTC

(Real Time Clock) gestire le funzioni ausiliarie di base e “sve-

glia” il sistema su base periodica per una verifica dell’attività.

Ad esempio un sistema può “svegliarsi” ogni secondo per ve-

rificare eventuali variazioni delle condizioni esterne e attiva-

re completamente il core del processore nel caso il software

debba eseguire l’elaborazione degli ingressi. Un approccio

di questo tipo, basato sull’interrogazione ciclica (polling) può

risultare dispendioso, in termini energetici, per tutti questi

sistemi in cui le condizioni di allerta sono rare e non si mani-

festano a intervalli regolari.

È possibile ottenere risposte più rapide a interrupt di tipo

casuale nel caso un sistema adotti uno stato di “sleep” a più

elevate energia per elaborare gli I/O e “svegliare” in tempi

brevi il core del processore nel caso si verifichi il supera-

mento di una soglia: queste modalità, in ogni caso, possono

assorbire la riserva di energia e non garantire al processore

la potenza necessaria per fornire una risposta. In ogni caso

è possibile abbinare le migliori caratteristiche della modalità

“deep-sleep” assicurando nel contempo la rapidità di rispo-

sta necessaria quando gli ingressi lo richiedono.

Sono disponibili RTC a bassissimo consumo che possono ve-

rificare l’esistenza di eventuali problematiche esterne, come

ad esempio problemi provocati da interrupt hardware o da

variazioni della tensione di ingresso rilevate da un compa-

ratore. Nel momento in cui è rilevato un evento esterno, il

sistema può “svegliarsi” velocemente senza nessuna penaliz-

zazione in termini di consumi imputabili all’implementazione

di una strategia di polling, ottimizzando in tal modo il periodo

di tempo che il sistema trascorre in modalità “deep sleep”.

Durante l’elaborazione software è importante assicurarsi

che venga svolta la massima quantità di lavoro possibile per

ogni ciclo di clock. In molte applicazioni IoT che prevedono

l’impiego di sensori è richiesto l’uso di algoritmi per l’elabo-

razione del segnale al fine di rilevare eventuali problemi ed

effettuare la pre-elaborazione dei dati prima che questi siano

trasferiti agli utilizzatori o al cloud.

Ciò, richiede non solo l’uso di architetture processore a 32

piuttosto che a 8 bit, capaci di eseguire operazioni matema-

tiche utilizzando un numero inferiore di cicli di clock, ma an-

che di architetture in grado di supportare istruzioni di ela-

borazione del segnale in virgola fissa e in virgola mobile. Il

supporto hardware per l’aritmetica in virgola mobile assicu-

ra l’esecuzione degli algoritmi in un numero di cicli di clock

nettamente inferiore, consentendo così al core di ritornare

velocemente in uno stato di “sleep” più efficiente in termini

energetici con conseguente riduzione dei consumi a livello

di sistema complessivo. Per soddisfare tutti questi requisiti è

necessario scegliere processori come Cortex-M4F di ARM,

utilizzati dai microcontrollori della famiglia Apollo di Ambiq.

Grazie ai miglioramenti apportati in termini di efficienza

energetica – a livello sia di sistema sia di funzionamento dei

circuiti a basso livello grazie ad un controllo accurato della

tensione – le tecnologie di energy harvesting si stanno pro-

ponendo come una valida alternativa per un numero sempre

crescente di progetti basati su sensori per applicazioni IoT.

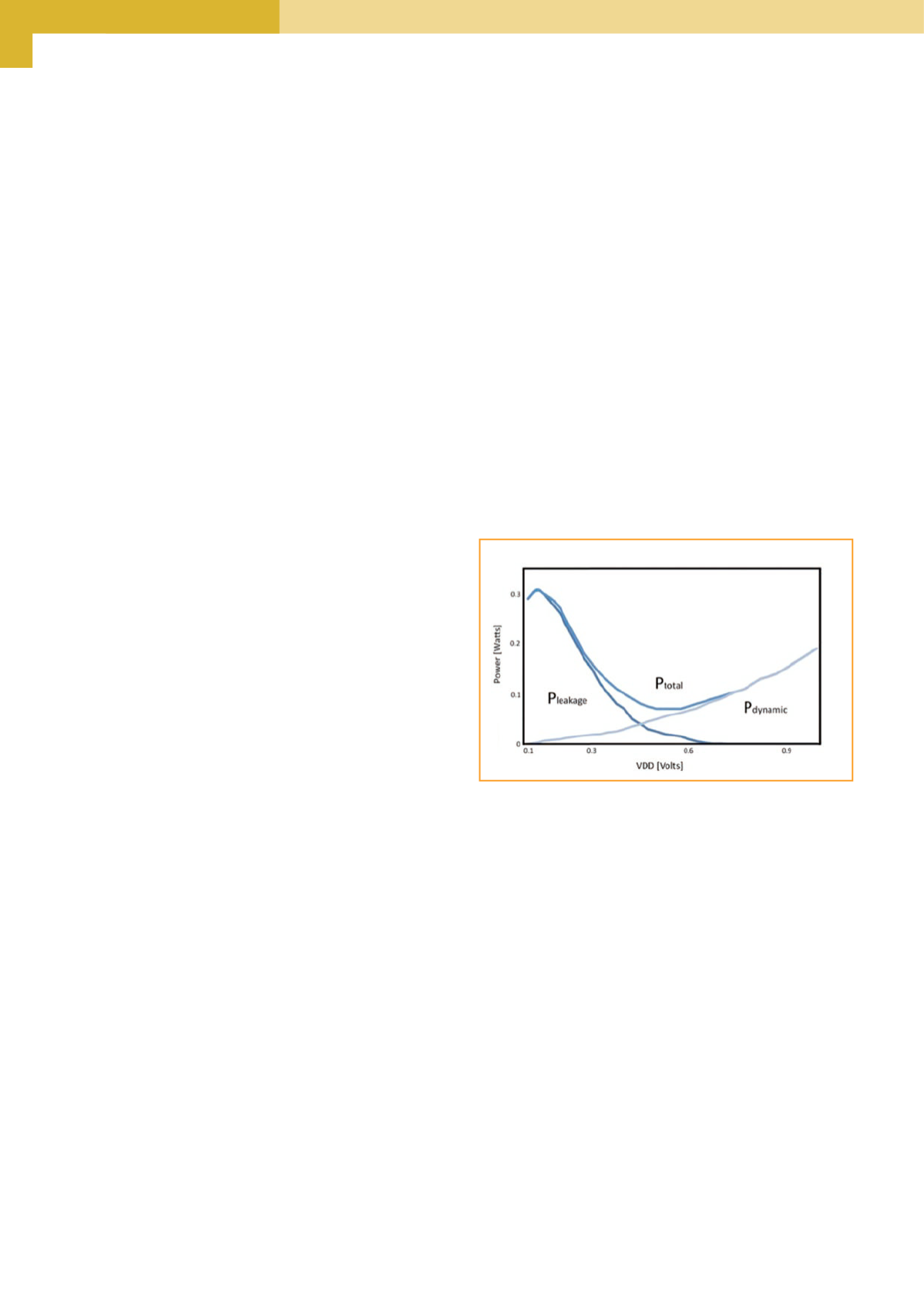

Fig. 2 – Per valori bassissimi della tensione le perdite per dispersione

tendono a essere predominanti