DIGITAL

SoC

54

- ELETTRONICA OGGI 447 - LUGLIO/AGOSTO 2015

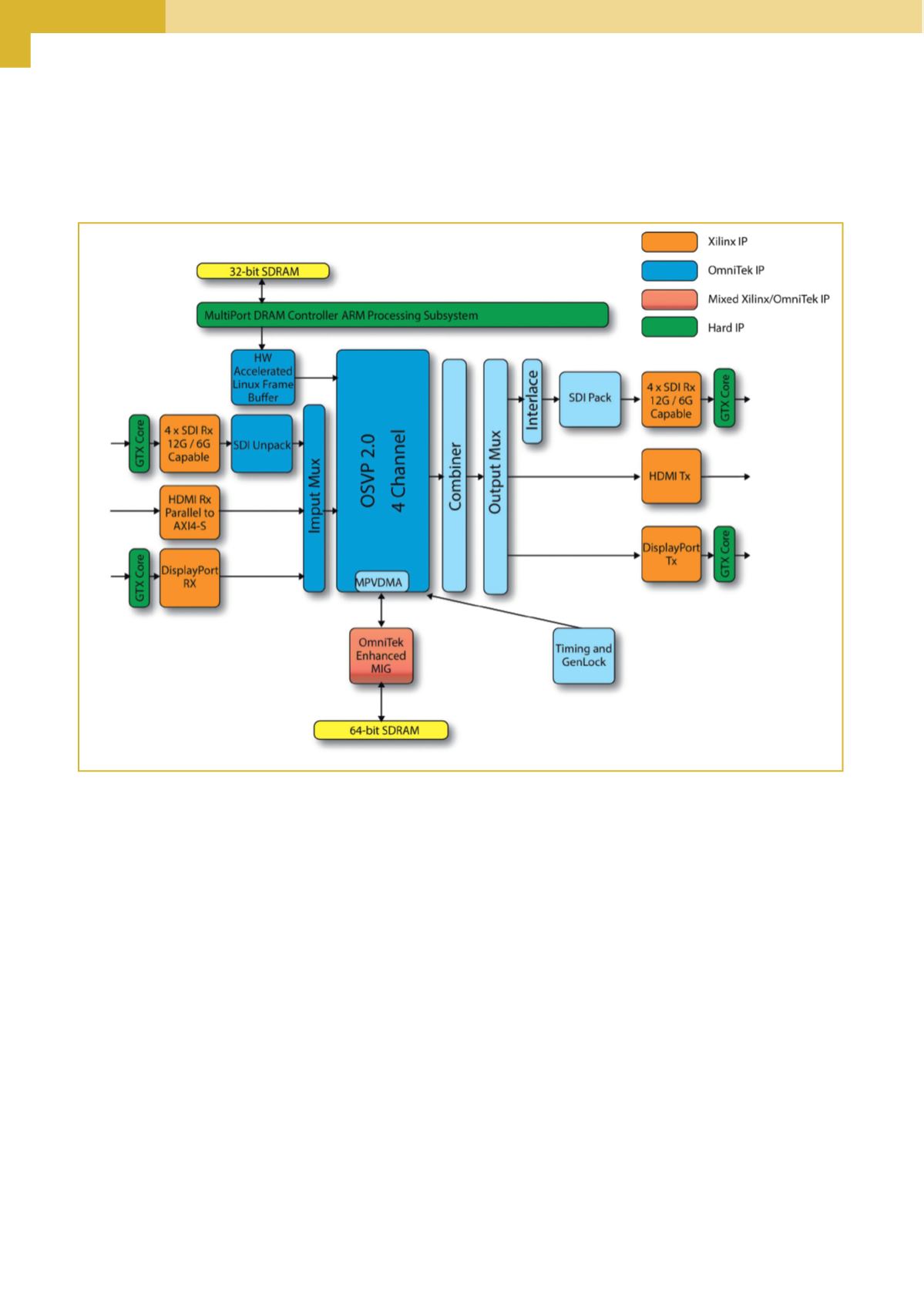

mi 4K: il processore video scalabile OSVP v2 di Omnitek e il

controllore DMA Multi-Canale, entrambi disponibili in versio-

ne ottimizzata per gli FPGA della serie 7 di Xilinx e per i SoC

Zynq. I due blocchi adottano gli standard di interconnessio-

ne a livello di sistema AMBA AXI4 di ARM.

Le risorse dell’ OSVP v2 includono correzione del colore su

sei assi; deinterlacciamento adattativo rispetto al movimento

e ai contorni (corredato da funzioni di rilevamento e di ela-

borazione della cadenza di ripresa a 3:2 e a 2:2); capacità

di ridimensionare e ritagliare l’immagine con miglioramento

della definizione, pulizia dell’immagine e riduzione del rumo-

re. Il blocco OSVP v2 include inoltre un blocco Video DMA

multi-porta che si propone come un’unità ad alta efficienza

per la gestione degli ingressi e delle uscite video. Nella figura

1 è schematizzata l’architettura dei canali in ingresso dell’u-

nità processore video scalabile OSVP v2 di OmniTek.

Il controllore DMA a flusso continuo multicanale è realizzato

in modo tale da consentire al controllore di usare in modo

efficiente la banda PCIe, ad esempio prelevando anticipata-

mente i descrittori da aree di memoria non contigue (modali-

tà scatter-gather) e riunendo pacchetti TLP consecutivi.

I vantaggi delle soluzioni programmabili

Sotto tre diverse forme, Xilinx offre un ulteriore supporto ai

progettisti di sistemi video 4K basati su FPGA e SoC.

Innanzitutto il SoC Zynq, un “mix” ottimale di capacità di ela-

borazione hardware e software per l’elaborazione video o

delle immagini ad alte prestazioni. Esso integra un sistema di

elaborazione ARM Cortex-A9 a due core ricco di funzionalità

e logiche programmabili FPGA della serie 7 (in tecnologia da

28 nanometri) in un singolo dispositivo. Gli utenti possono

far girare gli algoritmi di elaborazione sui processori ARM,

oppure trasferirli su hardware FPGA quando è richiesta l’ac-

celerazione per ottenere il funzionamento in tempo reale.

La velocità di elaborazione video di 300 MHz, offerta dalla

logica programmabile – sia degli FPGA Kintex 7 sia dei SoC

Zynq – combinata con le prestazioni di memoria di una DDR3

da 64 bit a 1600 Mbps, è critica per gestire l’elaborazione

Fig. 3 – Schema di massima della struttura del progetto di riferimento del sistema video RTVE 3.1