21

- ELETTRONICA OGGI 447 - LUGLIO/AGOSTO 2015

TECH INSIGHT

FPGA

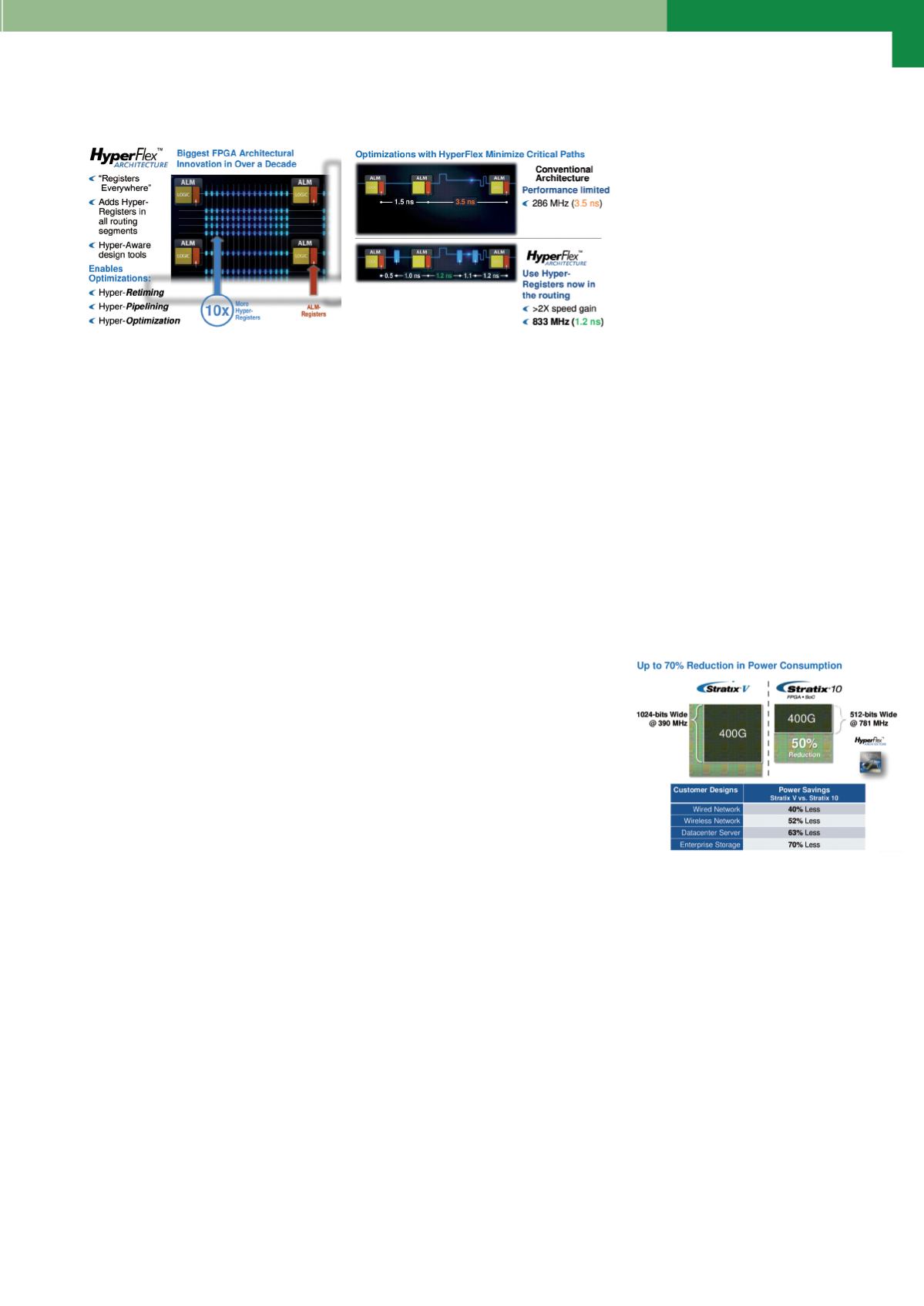

ture concorrenti. In aggiunta, la società sottolinea che l’architet-

tura HyperFlex permette ai sistemi ad alte prestazioni di operare

con consumi fino al 70% inferiori.

Package SiP 3D altamente integrato

Un altro aspetto importante da considerare, ricorda l’azienda, è

che tutti gli FPGA e i SoC della serie Stratix 10 sfruttano la capac-

ità d’integrazione di tecnologie eterogenee fornita dai package

SiP (system-in-package) 3D, che utilizzano la tecnologia EMIB

(embedded multi-die interconnect bridge) sviluppata da Intel. La

tecnologia SiP 3D permette di integrare con efficienza ed eco-

nomicità i core monolitici e ad alta densità (fino a 5,5 milioni di

elementi logici) con altri componenti evoluti, incrementando così

la scalabilità, la flessibilità e, come spiegato prima, l’efficienza dei

dispositivi Stratix 10, rispetto a quelli che si basano sull’uso di

molteplici die di FPGA per fornire densità più elevate.

L’integrazione eterogenea in package SiP 3D è appunto abilitata

dall’adozione della tecnologia proprietaria EMIB di Intel, che for-

nisce performance più elevate, riduce la complessità, abbassa i

costi e innalza l’integrità del segnale in confronto agli approcci

’interposer-based’. Altera aggiunge inoltre che i primi dispositivi

Stratix 10 utilizzeranno EMIB per integrare transceiver seriali ad

alta velocità e ’protocol tiles’ con la logica monolitica dei core.

L’implementazione di protocolli e transceiver ad alta velocità at-

traverso l’approccio 3D SiP consentirà ad Altera di rendere dis-

ponibili sul mercato in tempi brevi differenti versioni dei dispos-

itivi Stratix 10, per indirizzare la dinamica domanda del mercato.

Ad esempio, l’uso dell’integrazione eterogenea 3D SiP fornisce ai

dispositivi Stratix 10 un percorso di evoluzione per il supporto di

transceiver con velocità più elevate (56 Gbps), formati di mod-

ulazione emergenti (PAM-4), nuovi standard di comunicazione

(PCIe Gen4, Multi-Port Ethernet) e altre funzionalità, come memo-

ria a banda elevata o componenti analogici.

SoC FPGA: al cuore un ARM Cortex-A53

A prescindere dalla densità, tutti i SoC FPGA della linea Stratix 10

integrano un HPS (hardware processor system) basato su pro-

cessore quad-core ARM Cortex-A53 a 64 bit, equipaggiato con

un insieme completo di periferiche, che include un’unità di ge-

stione della memoria di sistema, controller di memoria esterna e

interfacce di comunicazione ad alta velocità. Con i SoC Stratix 10,

l’obiettivo di Altera è estendere la presenza nel settore dei SoC

FPGA di fascia alta. Le doti di versati-

lità, adattabilità, prestazioni, efficienza

di questa piattaforma di computing la

posizionano sul mercato per l’adozione

in un’ampia gamma di applicazioni ad

elevate performance: ad esempio, gli

sviluppatori di sistema possono usare i

SoC della serie Stratix 10 nei sistemi ad

alte prestazioni, per abilitare la virtua-

lizzazione dell’hardware, e al contempo aggiungere funzioni di

monitoraggio e gestione (pre-processing accelerazione, debug e

aggiornamento remoti, configurazione e monitoraggio delle pre-

stazioni del sistema).

Dal punto di vista dei consumi, tutta la gamma di FPGA e SoC

Stratix 10 può far leva sulle soluzioni di potenza PowerSoC di

Enpirion - la società acquisita da Altera circa due anni fa - oppor-

tunamente ottimizzate e validate per queste linee di dispositivi e

per soddisfare stringenti requisiti in termini di prestazioni e con-

sumi. Con i PowerSoC Enpirion, i risparmi realizzabili nei consu-

mi di energia della serie Stratix 10, rispetto alla generazione di

prodotti Stratix V, a seconda del settore di applicazione dei chip

(reti wired, reti wireless, server di data center, storage enterpri-

se), possono andare dal

40% al 70%.

Focus sulla security

I SoC e gli FPGA della

gamma Stratix 10 sono

anche equipaggiati con

una serie di funzionalità

di protezione. Innanzitut-

to, c’è il Secure Design

Manager (SDM), che

supporta la cifratura e

l’autenticazione basata

su settori; sono poi in-

tegrate l’autenticazione

MFA (multi-factor authentication - autenticazione multipla) e

la tecnologia PUF (physically unclonable function). Gli elevati

livelli di sicurezza dei dispositivi Stratix 10, sottolinea Altera,

posizionano questi prodotti come soluzioni adatte in applica-

zioni in campo militare, e nei progetti di security per il cloud e

le infrastrutture IoT.

Infine, la società pone una specifica attenzione anche sulla

componente software: il nuovo engine Spectra-Q integrato nel

software Quartus II è stato espressamente sviluppato per mas-

simizzare i vantaggi a livello di prestazioni, consumi e riduzio-

ne dell’ingombro (footprint) ottenibili con l’architettura Hyper-

Flex e, allo stesso tempo, per migliorare la produttività degli

ingegneri e il time-to-market dei progetti basati sugli FPGA e

SoC Stratix 10.

n

Fig. 4 – Nella gamma Stratix 10 la riduzio-

ne dei consumi può arrivare fino al 70%

Figg. 2-3 – L’architettura della tecnologia HyperFlex