27

- ELETTRONICA OGGI 447 - LUGLIO/AGOSTO 2015

il cancro. I neutroni abbinati

al fascio di fotoni utilizzati nel

trattamento danno luogo a

un flusso di neutroni termici

responsabile di un alto tas-

so di errori soft. In ogni caso

i neutroni termici non sono

oggigiorno la causa princi-

pale degli errori soft, poiché

i produttori hanno eliminato i

dielettrici borati a partire dal

nodi di processo a 150 nm.

Tecniche per evitare

gli errori soft

Gli errori soft possono essere

evitati migliorando la tecnolo-

gia di processo e il layout della

cella di memoria, apportando

modifiche a livello di siste-

ma e cambiando architettura

e tecniche di progettazione

dei chip. L’affidabilità di un

dispositivo di memoria può

essere migliorata tramite l’in-

cremento della carica critica

immagazzinata nella cella di

memoria. La “resistenza” di un

dispositivo agli errori soft può

essere aumentata utilizzando

una tecnologia di processo

che riduce lo spessore dello

strato di diffusione. Ciò per-

mette di diminuire il periodo

di tempo che una particella

carica trascorre nella cella

di memoria. Un’architettura

di tipo triple-well può essere

anche utilizzata per allonta-

nare le cariche dalla regione

attiva. Questo processo crea

un campo elettrico opposto

rispetto alla regione di svuota-

mento del transistor NMOS e

forza le cariche nel substrato.

Esso agisce solamente quan-

do un errore soft si verifica

nella regione NMOS. A livello

di sistema un progettista può

prevenire gli effetti dei soft

error utilizzando una logica

ECC (Error Correction Code)

esterna. L’adozione di questa

tecnica comporta l’uso di chip

di memoria aggiuntivi con

bit di parità per il rilevamen-

to e la correzione dell’errore.

Come previsto, l’attenuazione

a livello di sistema è costosa

e aumenta la complessità sia

del sistema stesso sia del sof-

tware.

Codici ECC

e bit interleaving

L’utilizzo della logica ECC rap-

presenta comunque il metodo

migliore per contrastare gli

errori soft. Durante un’opera-

zione di scrittura l’algoritmo

di codifica ECC include bit di

parità associato a ogni parola

indirizzabile dei dati imma-

gazzinati in memoria. Durante

un’operazione di lettura, l’al-

goritmo di rilevamento ECC

utilizza I bit di parità per de-

terminare se qualcuno dei bit

dei dati e cambiato. Se sus-

siste un errore su un singolo

bit, l’algoritmo di correzione

ECC determina la posizione

del bit interessato. Esso può

quindi semplificare la corre-

zione dell’errore commutan-

do il bit dei dati al suo valore

complementare. La tecnica

ECC non può essere utilizzato

in presenza di fenomeni MBU

(Multiple-Bit Upset). In questo

caso i progettisti devono ricor-

rere alla tecnica denominata

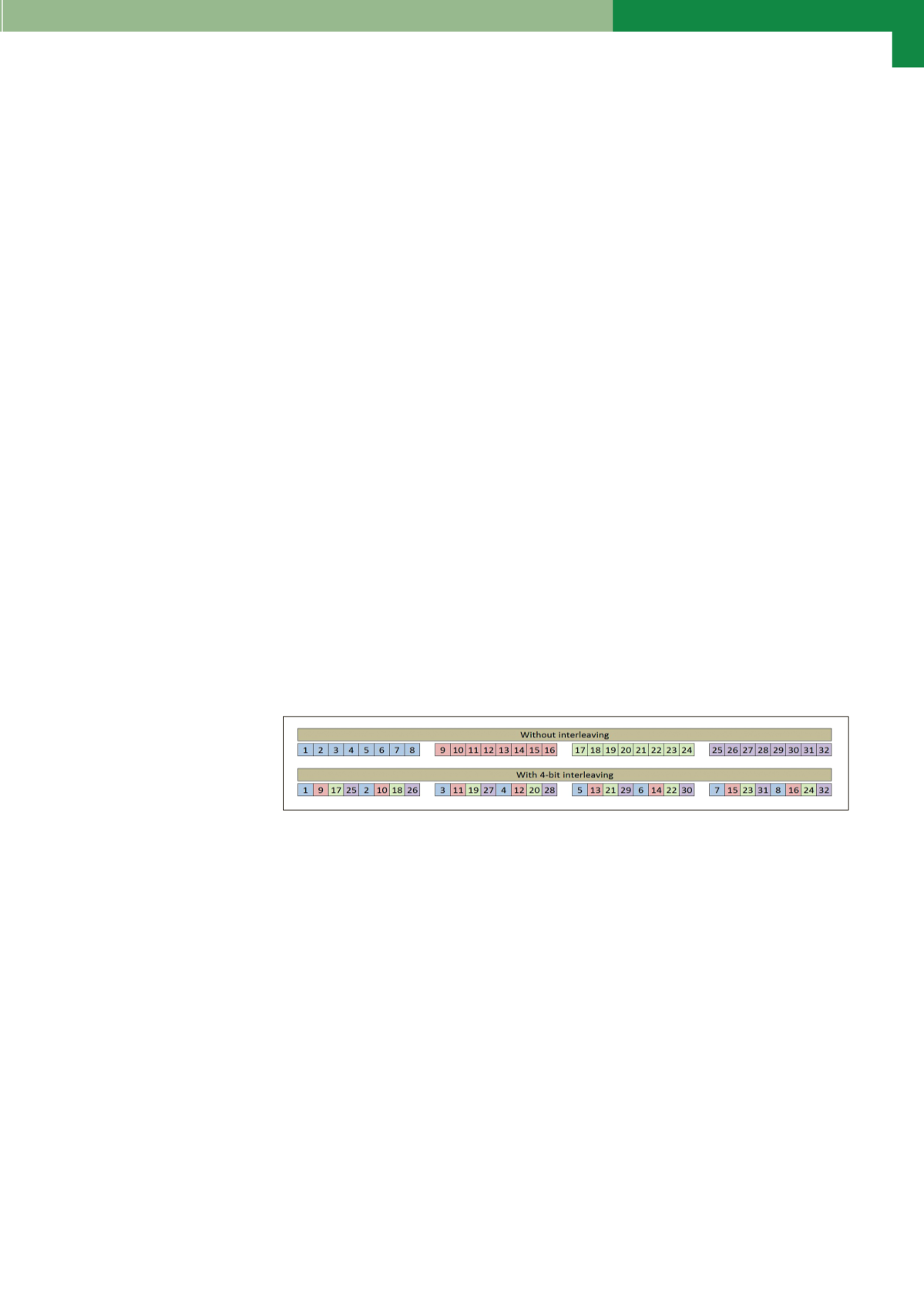

“bit interleaving”. Questa pre-

vede che le linee dei bit siano

disposte in modo tale che i bit

fisicamente adiacenti siano

mappati in differenti registri di

parola. La distanza tra i bit in-

tercalati (bit interleave distan-

ce) separa due bit consecutivi

mappati nello stesso registro

di parole (Fig. 3). Con una scel-

ta oculata di questa distanza

(che deve essere superiore

rispetto all’ampiezza delle cel-

le interessate dall’interazione),

è possibile ottenere un SBU

in più parole piuttosto che un

MBU in una singola parola.

La distanza tra i bit intercalati

dipende dalla tecnologia di

processo. In una memoria che

adotta il bit interleaving, l’algo-

ritmo di correzione dell’errore

su un singolo bit può essere

utilizzato per rilevare e correg-

gere tutti gli errori. L’algoritmo

ECC si applica solo alla copia

della parola di dati coinvolta.

Poiché il dato risiede nellame-

moria, contiene ancora il bit

commutato. Se questo bit resi-

dente nella memoria non vie-

ne corretto, l’esposizione a un

altro fenomeno di bit flipping

nella medesima parola può

dar luogo a un upset su più

bit. Di conseguenza è impor-

tante che la logica ECC segna-

li il verificarsi e la correzione

di un upset su un singolo bit.

Il sistema può utilizzare questa

informazione per identificare

l’evento ed eseguire la riscrit-

tura del dato corretto.

Questa tecnica va sotto il

nome di memory scrubbing

(in pratica l’esame della me-

moria alla ricerca di guasti).

Poiché i dispositivi a semicon-

duttore sono realizzati utiliz-

zando processi caratterizzati

da geometrie sempre più ri-

dotte, il rischio che si verifichi-

no errori soft aumenta. Sono

molti a ritenere che questo

tipo di errori rappresenti un

ostacolo a un’ulteriore ridu-

zione delle geometrie di pro-

cesso, a meno che non si svi-

luppino nuove tecnologie in

grado di affrontare in maniera

efficace il problema.

Oltre a ciò, vista la sempre

maggiore pervasività della

tecnologia nella vita quotidia-

na, l’esigenza di affidabilità è

destinata ad aumentare. Ciò a

sua volta si traduce nella ne-

cessità di integrare la logica

ECC a bordo dei chip dei mod-

uli di memoria: non a caso tut-

ti i più importanti produttori

di memoria hanno iniziato a

fornire chip con ECC per sod-

disfare la “fame” crescente di

memorie ad alta affidabilità. In

considerazione del fatto che le

memorie SRAM sono utilizzate

in applicazioni che richiedono

elevate prestazioni, la corre-

zione dell’errore è una funzio-

nalità sempre più apprezzata

e richiesta dagli utilizzatori:

per questo motivo Cypress

ha a catalogo una famiglia di

memorie SRAM asincrone ad

altissima affidabilità con ECC

on chip che supportano la tec-

nica di bit interleaving.

n

TECH INSIGHT

SOFT ERROR

Fig. 3 – Esempio di applicazione della tecnica di interleaving