25

PROGETTO AXIOM |

In tempo reale

EMBEDDED

57 • SETTEMBRE • 2015

standard open-source e verrà utilizzata in due

dimostratori nell’ambito delle case intelligenti

(Smart Home) e della video sorveglianza. Uno

dei punti critici del progetto è quello di riuscire

a garantire una elevata potenza computazionale,

adattabile agli scenari d’uso (es. appartamento,

palazzo, quartiere, nel caso della smart home)

tramite l’interfacciamento di più board. Se si

considera lo stato dell’arte attuale, le soluzioni

utilizzabili per fornire maggiore potenza compu-

tazionale sono basate tipicamente su architettu-

re multi- e many- core. Ad esempio, progetti eu-

ropei come

ADEPT [2] e

P-SOCRATES[3] stanno

esplorando tecniche per fondere assieme in modo

originale i risultati della comunità High-Perfor-

mance Computing (HPC) e quelli della comunità

Embedded (tradizionalmente focalizzate su im-

plementazioni performanti), con i risultati otte-

nibili con GPU (o dalle nuove architetture Data-

flow come

Maxeler [4] ) o con FPGA, tipicamente

più efficienti dal punto di vista dei consumi. Per

questo motivo, la ricerca portata avanti nel cor-

so del progetto AXIOM non sarà limitata a un

solo tipo di tecnologia, ma partirà da architetture

multicore efficienti dal punto di vista de consumi,

come le piattaforme ARM, e dagli acceleratori

FPGA integrati assieme in architetture come la

Xilinx Zinq.

Approccio tecnologico

Programmabilità del sistema e gestione del

parallelismo

In passato, le toolchain per CPS sono state svi-

luppate in modo dedicato per uno specifico do-

minio applicativo, spesso utilizzando dei costosi

software development kit.

Esempi recenti come Raspberry PI e

UDOO(quest’ultimo fondato da due dei partner del pro-

getto AXIOM) rappresentano esempi di succes-

so che riducono notevolmente i passi necessari

per apprendere una nuova tecnologia, fornendo

dispositivi a costi limitati sfruttando open har-

dware e software open-source.

Il basso costo e la semplicità di programmazione

aprono di fatto l’utilizzo di queste architetture a

comunità ampie formate non solo da esperti ma

anche da utenti finali del mondo educational e/o

maker.

Varie soluzioni sono state proposte nell’ultima

decade per permettere una semplice program-

mazione di algoritmi paralleli necessari per ot-

tenere un uso efficiente delle moderne architet-

ture multicore. Purtroppo, per ora, non si è crea-

to un consenso unanime su quale sia la migliore

soluzione disponibile.

Nell’ambito del progetto AXIOM ci si baserà

I partner del progetto

- Università di Siena (UNISI)

[5]

, coordinatore

del progetto, con competenze nell’ambito della

progettazione e valutazione di sistemi ad alte

prestazioni (es. progetto TERAFLUX

[1][16]

) ed

embedded e inoltre nel campo dell’interaction

design. Recentemente coordinatori.

- Barcelona Supercomputing Center (BSC)

[6]

,

segue lo sviluppo della toolchain software basa-

ta sul modello di progammazione OmpSs.

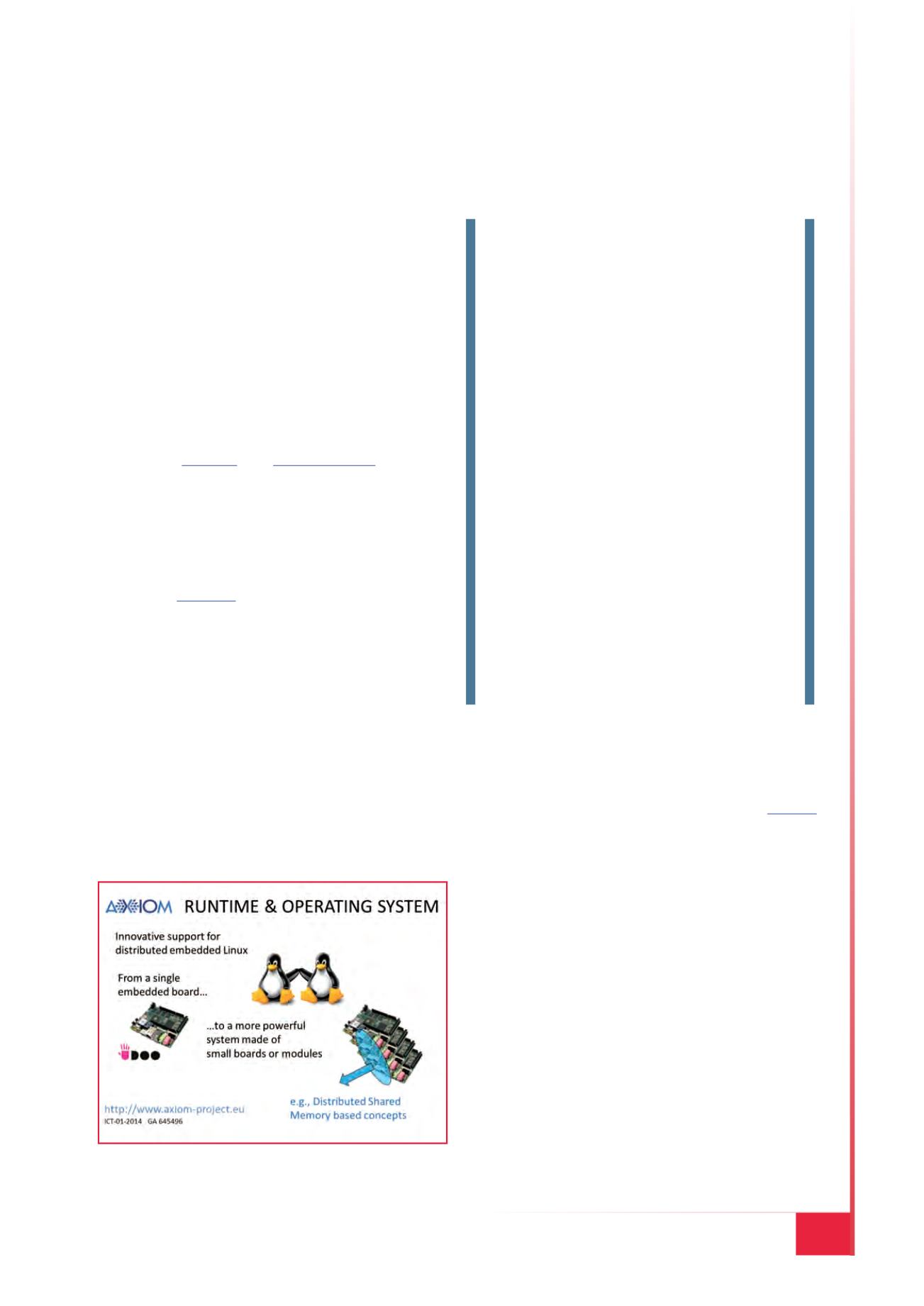

- Evidence

[7]

, si occuperà dello sviluppo del-

la piattaforma runtime nonché dell’adatta-

mento del sistema operativo Linux con l’im-

plementazione di una distributed shared

memory.

- SECO

[8]

, si occuperà di realizzare la scheda

hardware del progetto, con l’aiuto del part-

ner

FORTH

[9]

che fornirà il modulo FPGA di

interconnessione ad alta velocità (intorno ai

10Gbps) tra le board.

- Herta Security

[10]

e Vimar

[11]

, che si occu-

peranno dello sviluppo dei dimostratori in am-

bito rispettivamente della video sorveglianza e

smart home.

Fig. 2 – Da una singola board embedded è pos-

sibile ottenere un supercomputer connettendo

le varie board