Alimentazione: alcuni suggerimenti (parte 43) – I dispositivi discreti possono rappresentare una valida alternativa ai driver MOSFET integrati (parte 2 di 2)

Nel Power Tip 42 abbiamo analizzato un inseguitore di emettitore utilizzato per i circuiti di comando di gate MOSFET, mostrando come è possibile ottenere correnti di comando in un intervallo di 2 Amp grazie a piccoli transistor SOT-23.

In questo Power Tip, esamineremo i raddrizzatori sincroni autocomandati e discuteremo se è necessario ricorrere a driver discreti per proteggere i gate dei raddrizzatori sincroni dalle tensioni eccessive. In una situazione ideale, i raddrizzatori sincroni verrebbero comandati direttamente dal trasformatore di alimentazione. Tuttavia, in presenza di ampie variazioni della tensione di ingresso, la tensione del trasformatore potrebbe risultare elevata al punto di danneggiare i raddrizzatori sincroni.

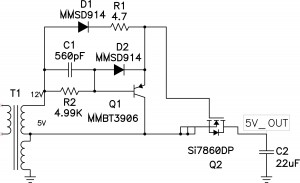

La figura 1 mostra un driver discreto utilizzato per controllare la conduzione del Q2 in un flyback sincrono. Tale circuito fornisce una corrente di gate con attivazione controllata e protegge il gate del raddrizzatore dalla tensione inversa elevata. Il circuito inizia con una tensione negativa sulle uscite del trasformatore.

L’uscita da 12 Volt risulta più negativa rispetto all’uscita da 5 Volt, portando il Q1 a condurre e cortocircuitare il gate-source di tensione sul FET di potenza Q2, spegnendolo rapidamente. Dato che la corrente di base fluisce attraverso R2, è presente una tensione negativa sul C1 del condensatore di accelerazione. Durante tale periodo di tempo, il FET primario conduce e immagazzina energia nell’induttanza magnetizzante del trasformatore. Quando il FET primario si spegne, la tensione di uscita del trasformatore oscilla in positivo. Il gate-source del Q2 viene rapidamente polarizzato in diretta attraverso il D1 e l’R1, causando la conduzione del Q2. La giunzione base-emitter del Q1 viene protetta dal D2 con la scarica del C1. Il circuito rimane in questo stato fino alla riattivazione del FET primario.

In realtà, la corrente di uscita può scaricare i condensatori di uscita come avverrebbe con un buck sincrono. L’attivazione del FET primario fa collassare la tensione sul secondario del trasformatore ed elimina il comando positivo dal Q2. Tale transizione può comportare uno shoot through significativo dalla sovrapposizione del tempo di conduzione del FET primario e del Q2. Per ridurre al minimo il tempo di attivazione dei FET primario e secondario, il Q1 cortocircuita il gate-source sul Q2 del raddrizzatore sincrono il più rapidamente possibile.

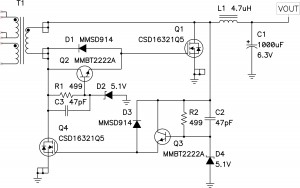

La figura 2 mostra un driver discreto utilizzato per controllare la conduzione del Q1 e del Q4 in un convertitore avanzato sincrono. In questa particolare progettazione, la tensione di ingresso ha un ampio intervallo. Ciò significa che i gate dei due FET potrebbero essere soggetti a tensioni superiori ai rispettivi valori nominali, pertanto si rende necessario un circuito di blocco. La configurazione di questo circuito attiva il Q4 quando la tensione di uscita del trasformatore risulta positiva, inoltre attiva il Q1 quando la tensione risulta negativa.

I diodi D2 e D4 limitano il comando positivo a circa 4,5 Volt. I FET vengono disattivati attraverso il D1 e il D3, comandati dal trasformatore e dalla corrente nell’induttore. Le tensioni di gate inverse vengono bloccate a terra mediante il Q1 e il Q4. In questa particolare progettazione, i FET presentano capacità di gate di valore relativamente ridotto, pertanto le transizioni risultano rapide. FET di dimensioni maggiori richiedono l’implementazione di un transistor PNP per disaccoppiare la capacità di gate dall’avvolgimento del trasformatore e per migliorare la velocità di disattivazione. La scelta del package corretto per il Q2 e il Q3 dei transistor di comando di gate risulta critica, dato che in tali transistor la potenza dissipata potrebbe essere elevata, in quanto fungono da regolatori lineari durante la carica delle capacità dei gate FET. Inoltre, in presenza di tensioni di uscita superiori, la pote dissipata in R1 e R2 può risultare considerevole.

Riepilogando, molte alimentazioni con raddrizzatori sincroni possono utilizzare la tensione di avvolgimento del trasformatore per comandare i gate dei raddrizzatori sincroni. Ingressi con intervalli ampi o tensioni di uscita elevate richiedono la protezione dei gate da parte dei circuiti di condizionamento. Nel flyback sincrono illustrato in figura 1, abbiamo mostrato come è possibile bloccare la tensione inversa sul gate del raddrizzatore sincrono, pur preservando transizioni rapide di commutazione. In modo simile, nell’avanzamento sincrono di figura 2, abbiamo mostrato come limitare la tensione di comando positiva sui gate dei raddrizzatori sincroni.

Nel prossimo incontro analizzeremo gli elevati transitori di carico di/dt e le relative implicazioni nella progettazione e nel test di alimentazioni adeguate.

Per ulteriori informazioni su questa e altre soluzioni per gli alimentatori, visitare: http://www.ti.com/power-ca

Per contattare Robert Kollman: powertips@list.ti.com

Leggi tutti i corsi

Robert Kollman, Texas Instruments

Contenuti correlati

-

Progettazione di un circuito di precarica attiva con condensatore DC-Link ad alta tensione

Questo articolo presenta il processo di progettazione necessario per calcolare gli adeguati valori dei componenti che contribuiscono a ottenere il profilo di carica desiderato Leggi l’articolo completo su EO 521

-

I miglioramenti nella tecnologia RFID danno origine a nuove applicazioni

L’identificazione a radiofrequenza (RFID) è una tecnologia consolidata che viene impiegata da molti anni, con l’introduzione dei primi esempi di transponder RF passivi che risale agli anni 70. Probabilmente la usate tutti i giorni senza accorgervene, ma...

-

TI presenta i suoi nuovi PLD

Texas Instruments (TI) ha presentato nuovi dispositivi a logica programmabile (PLD) che permettono di semplificare e velocizzare lo sviluppo di progetti di dispositivi logici per qualsiasi tipo di applicazione. È possibile integrare fino a 40 combinazioni e...

-

Come migliorare la sicurezza negli inverter di trazione dei veicoli elettrici

I progettisti di veicoli elettrici possono aumentare la sicurezza e l’affidabilità dei sistemi a inverter di trazione monitorando la soglia di tensione del gate Leggi l’articolo completo su EO520

-

Finanziamenti per 1,6 miliardi per Texas Instruments

Texas Instruments (TI) ha firmato un memorandum d’intesa preliminare non vincolante con il Dipartimento del Commercio degli Stati Uniti per un finanziamento diretto fino a 1,6 miliardi di dollari. Questa operazione rientra nell’ambito del CHIPS and Science...

-

Un processore con LPDDR4 integrata accelera lo sviluppo di applicazioni

Il System-in-Package rappresenta una valida scelta di progettazione e può essere determinante per lo sviluppo di svariate applicazioni e dispositivi di tipo general purpose, nonché per soluzioni compatte e ad alte prestazioni Leggi l’articolo completo su EO519

-

I vantaggi dell’analogico e del digitale per la soluzione LogiCoA di ROHM

ROHM ha creato LogiCoA, una innovativa soluzione di alimentazione per apparecchiature industriali e consumer di piccola e media potenza (da 30 W a 1 kW) che fornisce le stesse funzionalità degli alimentatori con controllo completamente digitale a...

-

Progettazione di un’applicazione per supportare ampi intervalli di tensione di ingresso e della batteria

Oltre a contribuire a ridurre i tempi di progetto, l’utilizzo di un caricabatterie ad ampio VIN e ampia VOUT permette di valutare nuove tecnologie, come la ricarica bidirezionale a energia solare Leggi l’articolo completo su EO519

-

Texas Instruments e Delta Electronics insieme per le soluzioni per EV

Texas Instruments (TI) ha stretto una collaborazione a lungo termine con Delta Electronics per creare soluzioni di ricarica di bordo e alimentazione di nuova generazione per veicoli elettrici (EV). Questa collaborazione sfrutterà le capacità di ricerca e...

-

Power Integrations amplia l’offerta di driver per motori BLDC

BridgeSwitch-2 è una nuova famiglia di driver per motori elettrici BLDC realizzata da Power Integrations. Questi componenti con architettura IHB (integrated half-bridge) sono concepiti per applicazioni fino a 1 CV (746 W) e consentono un’efficienza dell’inverter sino...