Alimentazione: alcuni suggerimenti (parte 41) – Potenziamento della memoria DDR

La dissipazione di potenza all’interno dei sistemi logici CMOS è principalmente correlata alla frequenza di clock, alla capacità di ingresso dei diversi gate inclusi nel sistema e alla tensione di alimentazione. Con il ridimensionamento delle dimensioni dei dispositivi, e quindi delle tensioni di alimentazione, sono stati ottenuti guadagni significativi nella riduzione della dissipazione a livello di gate. Queste ridotte dissipazioni, insieme al funzionamento a più alta velocità dei dispositivi a più alta frequenza, hanno consentito di confinare le frequenze di clock nell’intervallo dei gigahertz.

A frequenze di clock così alte, le impedenze controllate, i bus appropriatamente terminati e l’accoppiamento ottimale consentono di avere un segnale di clock appropriato. Tradizionalmente, i dispositivi logici sono stati progettati per eseguire il clock dei dati su un unico fronte del clock e quello della memoria DDR sia sul fronte in salita sia sul fronte in discesa del clock. In questo modo, è possibile raddoppiare la velocità di trasmissione dei dati con solo un aumento minimo a carico della dissipazione della potenza.

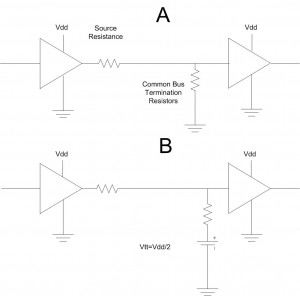

L’incrementata velocità dei dati richiede che la rete di distribuzione dei clock venga accuratamente progettata per ridurre al minimo le oscillazioni transitorie e le riflessioni , che potrebbero inavvertitamente eseguire il clock dei dispositivi logici. Nella figura 1 sono presentati due possibili schemi di terminazione dei bus. Nel primo (A), i resistori di terminazione dei bus sono posizionati alla fine della rete di distribuzione e sono collegati a terra. Se il driver dei bus è nello stato basso, la dissipazione dei resistori è pari a zero. Nello stato alto, la dissipazione di potenza dei resistori è uguale al quadrato della tensione di alimentazione (VDD) diviso la resistenza dei bus (impedenza di sorgente più resistore di terminazione). La perdita media equivale al quadrato della tensione di alimentazione diviso per il doppio della resistenza dei bus.

Nel secondo schema (B), il resistore di terminazione è collegato a una tensione di alimentazione (VTT) pari alla metà della tensione VDD. La dissipazione all’interno del resistore è quindi costante, indipendentemente dalla tensione di alimentazione, ed equivale al quadrato di VTT (o al quadrato di (Vdd/2)) diviso per la resistenza di terminazione. Il risultato è un fattore di riduzione pari a 2 per il risparmio di potenza rispetto al primo approccio, ma con il costo di un’alimentazione aggiuntiva.

Ad ogni modo, i requisiti per questa alimentazione sono fuori dalla norma. Innanzitutto, la relativa uscita deve essere la metà di quella della tensione del driver (VDD). Come seconda cosa, deve sia fornire sia raccogliere corrente. Quando la tensione di uscita del driver è bassa, la corrente fluisce dall’alimentazione VTT; quando la tensione del driver è alta, invece, la corrente fluisce nell’alimentazione. Infine, l’alimentazione deve passare tra diverse modalità man mano che cambiano i dati di sistema e deve fornire una bassa impedenza di sorgente, prossima alla frequenza di clock del sistema.

La potenza di picco è facilmente determinabile in base ai resistori di terminazione, alla frequenza di clock e alle capacità interne al sistema. Diversamente, la potenza media è più difficile da calcolare e può essere inferiore di molte volte a un decimo della potenza di picco. Questi fattori devono essere attentamente considerati perché il sistema è dinamico e non presenta una frequenza di clock fissa. Inoltre, il clock dei dati non viene eseguito ad ogni ciclo e alcuni dispositivi si troveranno in un terzo stato di alta impedenza.

Con le misure del sistema, è importante verificare il valore della corrente media in quanto può essere determinante per stabilire l’appropriata topologia dell’alimentazione. Ad esempio, si potrebbe valuatare la bassa dissipazione di potenza di un’alimentazione di commutazione con le dimensioni e il costo ridotti di un regolatore lineare. Nella tabella 1 vengono confrontati il numero di componenti, i requisiti di area, la dissipazione e il costo di un commutatore e di un regolatore lineare. I dati sono riferiti a regolatori in grado di generare 3 amp di corrente di picco. È interessante notare che, se la corrente di picco è sempre presente, la gestione della dissipazione diventa difficile. La scelta può essere effettuata stabilendo la corrente in CC. Evidentemente, il regolatore lineare è più vantaggioso sotto tutti gli altri aspetti.

Una questione importante che emerge con un’alimentazione DDR è il controllo della tensione di uscita durante carichi transitori incontrollati ed estremi. Come mostrato nella tabella 1, l’approccio lineare consente un controllo della larghezza di banda estremamente più accurato rispetto allo switching. Di conseguenza, è possibile utilizzare condensatori di dimensioni più ridotte per controllare l’impedenza di uscita. Per controllare l’uscita fino a 40 mV con un carico di 3 amp, ad esempio, l’impedenza di uscita in corrispondenza della frequenza di crossover deve essere inferiore a 0,013 ohm, il che corrisponde a circa 10 uF di capacità. Un switching dotato di un controllo a circuito chiuso a 50 Hz ha più di 200 uF di capacità, con un conseguente aumento dei costi e dell’area dei circuiti (vedere il Power Tip 10).

Per riepilogare, la memoria DDR migliora la velocità del sistema eseguendo il clock dei dati su entrambi i fronti del clock e consente quindi di incrementare la trasmissione. A causa del funzionamento ad alta frequenza, è necessario utilizzare resistori di terminazione per ridurre i riflessi di tensione. Le perdite nelle terminazioni possono essere ridotte al minimo collegando un’estremità a una tensione uguale alla metà della tensione di alimentazione. Questa alimentazione deve essere in grado di fornire o assorbire corrente e presentare un’elevata frequenza di crossover per minimizzare i requisiti dei condensatori. Un approccio basato su regolatore lineare per l’alimentazione delle terminazioni consente di risparmiare e di ridurre le dimensioni, purché l’aumento della dissipazione di potenza rimanga accettabile.

Nel prossimo incontro si discuterà di semplici circuiti di comando di gate FET.

Per ulteriori informazioni su questa e altre soluzioni per gli alimentatori, visitare: http://www.ti.com/power-ca

Per contattare Robert Kollman: powertips@list.ti.com

Leggi tutti i corsi

Robert Kollman, Texas Instruments

Contenuti correlati

-

USB Power Delivery: efficienza e convenienza per l’infotainment a bordo veicolo

I controllori USB PD di TI sono una soluzione su chip singolo che permette di migliorare l’efficienza e la densità di potenza dei prodotti USB destinati al mondo automotive Leggi l’articolo completo su EO Power 36

-

Il nuovo centro di distribuzione dei prodotti di TI

Texas Instruments (TI) ha aperto un nuovo centro per la distribuzione dei prodotti a Dreieich, nei pressi di Francoforte. Il nuovo impianto, che ha un’estensione di 9.000 metri quadrati, dispone di nuove funzionalità di automazione. Può infatti...

-

Progettazione di un circuito di precarica attiva con condensatore DC-Link ad alta tensione

Questo articolo presenta il processo di progettazione necessario per calcolare gli adeguati valori dei componenti che contribuiscono a ottenere il profilo di carica desiderato Leggi l’articolo completo su EO 521

-

I miglioramenti nella tecnologia RFID danno origine a nuove applicazioni

L’identificazione a radiofrequenza (RFID) è una tecnologia consolidata che viene impiegata da molti anni, con l’introduzione dei primi esempi di transponder RF passivi che risale agli anni 70. Probabilmente la usate tutti i giorni senza accorgervene, ma...

-

TI presenta i suoi nuovi PLD

Texas Instruments (TI) ha presentato nuovi dispositivi a logica programmabile (PLD) che permettono di semplificare e velocizzare lo sviluppo di progetti di dispositivi logici per qualsiasi tipo di applicazione. È possibile integrare fino a 40 combinazioni e...

-

Come migliorare la sicurezza negli inverter di trazione dei veicoli elettrici

I progettisti di veicoli elettrici possono aumentare la sicurezza e l’affidabilità dei sistemi a inverter di trazione monitorando la soglia di tensione del gate Leggi l’articolo completo su EO520

-

Finanziamenti per 1,6 miliardi per Texas Instruments

Texas Instruments (TI) ha firmato un memorandum d’intesa preliminare non vincolante con il Dipartimento del Commercio degli Stati Uniti per un finanziamento diretto fino a 1,6 miliardi di dollari. Questa operazione rientra nell’ambito del CHIPS and Science...

-

Un processore con LPDDR4 integrata accelera lo sviluppo di applicazioni

Il System-in-Package rappresenta una valida scelta di progettazione e può essere determinante per lo sviluppo di svariate applicazioni e dispositivi di tipo general purpose, nonché per soluzioni compatte e ad alte prestazioni Leggi l’articolo completo su EO519

-

I vantaggi dell’analogico e del digitale per la soluzione LogiCoA di ROHM

ROHM ha creato LogiCoA, una innovativa soluzione di alimentazione per apparecchiature industriali e consumer di piccola e media potenza (da 30 W a 1 kW) che fornisce le stesse funzionalità degli alimentatori con controllo completamente digitale a...

-

Progettazione di un’applicazione per supportare ampi intervalli di tensione di ingresso e della batteria

Oltre a contribuire a ridurre i tempi di progetto, l’utilizzo di un caricabatterie ad ampio VIN e ampia VOUT permette di valutare nuove tecnologie, come la ricarica bidirezionale a energia solare Leggi l’articolo completo su EO519