Alimentazione: alcuni suggerimenti (parte 31) – Scelta del giusto rapporto di resistenza dei MOSFET con buck sincrono

In questo Power Tip verrà esaminato uno studio sul trade-off della dissipazione della potenza di conduzione in uno stadio di potenza del buck sincrono in funzione del fattore di servizio e del rapporto tra le resistenze del FET.

I risultati di tale analisi rappresentano un punto di partenza utile per la selezione dei FET. Generalmente, come parte del processo di progettazione, viene fornito un insieme di specifiche che include una gamma di tensioni di ingresso e la tensione di uscita desiderata e viene chiesto di selezionare i FET.

Nel caso di progettisti di circuiti integrati, è possibile che venga rilasciato un budget comprendente il costo dei FET o la dimensione del package. Entrambi i dati consentono di selezionare l’intera area della piastrina (“die area”) MOSFET. Inoltre, tali dati possono essere utilizzati per ottimizzare le rispettive aree del FET in materia di efficienza.

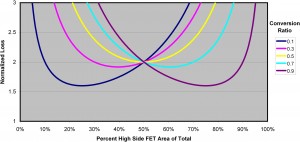

Fig 1 – La perdita di conduzione è una funzione tra i rapporti di resistenza dei FET e il fattore di servizio

A un primo ordine, la resistenza di un FET è inversamente proporzionale alla sua area. Pertanto, se vi è un’intera area allocata per i FET e viene ingrandito l’high side (per ridurne la resistenza), l’area per il low side viene ridotta con un conseguente aumento della resistenza.

In secondo luogo, la percentuale di tempo della conduzione dei FET high side e low side è relazionata al rapporto di conversione VOUT/VIN che a un primo ordine è pari al fattore di servizio (D, “duty factor”) dell’high side. Il FET high side conduce per una percentuale di tempo D, mentre il FET low side per la percentuale di tempo restante (1-D).

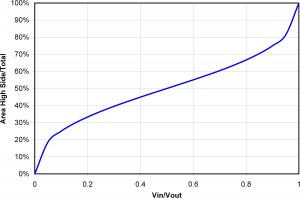

In figura 1 viene presentata una perdita di conduzione normalizzata come funzione tra la percentuale dell’area FET dedicata al FET high side (asse X) e il fattore di conversione (curve). Grazie ad alcuni rapporti di conversione, vi è un’ottima allocazione tra high e low side dell’area della piastrina, in cui si verifica una perdita di conduzione totale minima. In caso di rapporti di conversione ridotti, utilizzare un FET high side di dimensioni ridotte.Al contrario, in caso di rapporti elevati, utilizzare più FET nella parte superiore.

Le allocazioni si rivelano critiche se in un circuito ottimizzato per un rapporto di conversione da 12 a 1,2 volt (fattore di servizio pari al 10%) si verifica un aumento del 30% delle perdite di conduzione in corrispondenza di un aumento della tensione di uscita pari a 3,6 volt e perdite ulteriori fino all’80% se la tensione di uscita viene aumentata a 6 volt.

Infine, è utile sottolineare che ogni curva passa per lo stesso punto in corrispondenza dell’allocazione dell’area high side pari al 50%. Ciò avviene perché in quel punto le due resistenze del FET sono uguali.

Dalla figura 1 si evince che il peggiore dei casi di perdita di conduzione ottimizzata si verifica quando il rapporto di conversione è pari al 50%. Tuttavia, esiste la possibilità di ridurre le perdite al di sotto di questo livello a diversi rapporti di conversione.

Fig. 2 – È presente un’ottimo rapporto tra aree basato sul rapporto di conversione (Nota: i rapporti di resistenza sono l’inverso dei rapporti tra le aree)

In Appendice 1 vengono descritti i calcoli matematici per tale ottimizzazione, mentre in figura 2 vengono illustrati i risultati. Inoltre, anche in caso di rapporti di conversione estremamente bassi, è necessario dedicare una considerevole parte dell’area della piastrina del FET al FET high side. Ciò vale anche in caso di rapporti di conversione elevati: è necessario dedicare una parte consistente dell’area al FET low side.

Questi risultati sono delle osservazioni di prim’ordine al problema e non comprendono fattori quali una resistenza specifica diversa tra il FET high side e il FET low side, le implicazioni derivanti da velocità di commutazione o costi e resistenze associati al packaging dell’area della piastrina. Tuttavia, ciò rappresenta un valido inizio per stabilire i rapporti di resistenza tra i FET, al fine di operare una scelta migliore nella selezione dei FET.

Nel prossimo incontro discuteremo di come stabilire i requisiti di un’induttanza di dispersione per un induttore accoppiato utilizzato in SEPIC.

Per ulteriori informazioni su questa e altre soluzioni per gli alimentatori, visitare: www.ti.com/power-ca

Per contattare Robert Kollman: powertips@list.ti.com

Appendice: dalla figura 2

Alcune definizioni

Resistenza specifica MOSFET (Ohm*area): ρ

Area totale: A

Area del FET high side: α

Risoluzione della perdita di conduzione totale (valore utilizzato per la Fig. 1): ![]()

Calcolo della derivata rispetto ad α: ![]()

Definizione dell’high side sull’area totale del FET come (reciproco dei rapporti di resistenza). Impostazione dell’equazione precedente uguale a zero e sostituzione.

Dopo alcune pagine di calcoli: ![]()

I risultati sono disponibili in figura 2.

Contenuti correlati

-

USB Power Delivery: efficienza e convenienza per l’infotainment a bordo veicolo

I controllori USB PD di TI sono una soluzione su chip singolo che permette di migliorare l’efficienza e la densità di potenza dei prodotti USB destinati al mondo automotive Leggi l’articolo completo su EO Power 36

-

Il nuovo centro di distribuzione dei prodotti di TI

Texas Instruments (TI) ha aperto un nuovo centro per la distribuzione dei prodotti a Dreieich, nei pressi di Francoforte. Il nuovo impianto, che ha un’estensione di 9.000 metri quadrati, dispone di nuove funzionalità di automazione. Può infatti...

-

Progettazione di un circuito di precarica attiva con condensatore DC-Link ad alta tensione

Questo articolo presenta il processo di progettazione necessario per calcolare gli adeguati valori dei componenti che contribuiscono a ottenere il profilo di carica desiderato Leggi l’articolo completo su EO 521

-

I miglioramenti nella tecnologia RFID danno origine a nuove applicazioni

L’identificazione a radiofrequenza (RFID) è una tecnologia consolidata che viene impiegata da molti anni, con l’introduzione dei primi esempi di transponder RF passivi che risale agli anni 70. Probabilmente la usate tutti i giorni senza accorgervene, ma...

-

TI presenta i suoi nuovi PLD

Texas Instruments (TI) ha presentato nuovi dispositivi a logica programmabile (PLD) che permettono di semplificare e velocizzare lo sviluppo di progetti di dispositivi logici per qualsiasi tipo di applicazione. È possibile integrare fino a 40 combinazioni e...

-

Come migliorare la sicurezza negli inverter di trazione dei veicoli elettrici

I progettisti di veicoli elettrici possono aumentare la sicurezza e l’affidabilità dei sistemi a inverter di trazione monitorando la soglia di tensione del gate Leggi l’articolo completo su EO520

-

Finanziamenti per 1,6 miliardi per Texas Instruments

Texas Instruments (TI) ha firmato un memorandum d’intesa preliminare non vincolante con il Dipartimento del Commercio degli Stati Uniti per un finanziamento diretto fino a 1,6 miliardi di dollari. Questa operazione rientra nell’ambito del CHIPS and Science...

-

Un processore con LPDDR4 integrata accelera lo sviluppo di applicazioni

Il System-in-Package rappresenta una valida scelta di progettazione e può essere determinante per lo sviluppo di svariate applicazioni e dispositivi di tipo general purpose, nonché per soluzioni compatte e ad alte prestazioni Leggi l’articolo completo su EO519

-

I vantaggi dell’analogico e del digitale per la soluzione LogiCoA di ROHM

ROHM ha creato LogiCoA, una innovativa soluzione di alimentazione per apparecchiature industriali e consumer di piccola e media potenza (da 30 W a 1 kW) che fornisce le stesse funzionalità degli alimentatori con controllo completamente digitale a...

-

Progettazione di un’applicazione per supportare ampi intervalli di tensione di ingresso e della batteria

Oltre a contribuire a ridurre i tempi di progetto, l’utilizzo di un caricabatterie ad ampio VIN e ampia VOUT permette di valutare nuove tecnologie, come la ricarica bidirezionale a energia solare Leggi l’articolo completo su EO519