ARM e Cadence insieme per il processo FinFET

Annunciato dalle due società il primo tape-out del processore Cortex A57 a 64 bit su processo FinFET a 16 nm di TSMC

ARM e Cadence hanno annunciato la loro collaborazione per il primo tape-out del processore Cortex A57 di ARM, su processo FinFET a 16 nanometri di TSMC. Il chip di test è stato implementato utilizzando il flusso completo Cadence RTL-to-signoff, la piattaforma di progettazione custom Cadence Virtuoso, le librerie di celle standard ARM Artisan e le librerie di I/O, memorie e PLL (phase-locked loop) di TSMC.

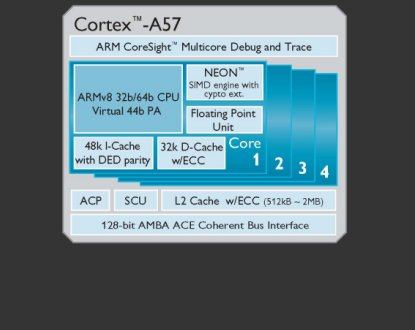

Cortex A-57 è il processore a più elevate prestazioni presente nella gamma di ARM ed è basato sul nuovo set di istruzioni a 64 bit denominato ARMv8, progettato per applicazioni di computing, networking e mobili che richiedono prestazioni elevate e bassi consumi. La tecnologia FinFET a 16 nanometri di TSMC rappresenta una svolta significativa per consentire la scalabilità continua della tecnologia di processo a dimensioni inferiori a 20 nm.

Il processo a 16 nanometri che impiega la tecnologia FinFET presentava nuove sfide che hanno richiesto lo sviluppo di importanti nuove funzionalità nei tool di progettazione. Nuove regole di progettazione, estrazione RC per transistor 3D, maggiore complessità dei modelli di resistenza per interconnessioni e vias, librerie di celle quantizzate, caratterizzazione delle librerie che supporta nuovi modelli di transistor e double-patterning su più strati sono solo alcune delle problematiche affrontate nei prodotti custom, digitali e di signoff di Cadence.

Contenuti correlati

-

Tecnologia CoWoS di TSMC per il nuovo sottosistema di Alphawave Semi

Alphawave Semi ha annunciato la disponibilità del primo sottosistema Die-to-Die (D2D) Universal Chiplet Interconnect Express (UCIe) a 3 nm basato sulla tecnologia di packaging avanzata Chip-on-Wafer-on-Substrate (CoWoS) di TSMC. Questo sottosistema, sviluppato in stretta collaborazione con TSMC,...

-

I DSP Tensilica di Cadence per l’audio di NXP

I DSP Tensilica HiFi 5 di Cadence sono diventati un componente chiave nell’ultima famiglia di DSP audio per autoveicoli di NXP Semiconductors, consentendo di implementare funzionalità audio avanzate per veicoli software-defined di nuova generazione. NXP ha infatti...

-

eMCOS POSIX di eSOL supporta il processore automotive Arm Cortex-R82AE

eSOL ha annunciato il supporto per il processore per il mercato automotive Arm Cortex-R82AE tramite il suo sistema operativo eMCOS POSIX. Questo risultato è stato reso possibile utilizzando prototipi virtuali dell’IP di Arm sotto Arm Virtual Hardware...

-

Partnership tra Altair e Samsung Electronics

Altair ha annunciato di essere stata scelta come partner per l’automazione della progettazione elettronica (EDA) per il Samsung Advanced Foundry Ecosystem (SAFE). Questa collaborazione permetterà di combinare la tecnologia EDA di Altair, compresi gli strumenti per il...

-

Come aumentare la sicurezza delle comunicazioni nei sistemi di ricarica dei veicoli elettrici

Nel caso dei veicoli elettrici, è possibile sfruttare diversi punti di attacco: uno che desta una crescente preoccupazione è l’infrastruttura di ricarica Leggi l’articolo completo su EO Power 34

-

Certificazione ISO 26262 per l’ambiente di progettazione FPGA di GOWIN

GOWIN Semiconductor ha annunciato che il suo ambiente di progettazione FPGA GOWIN EDA è stato certificato conforme agli standard di sicurezza funzionale ISO 26262 e IEC 61508 dal laboratorio di test TUV. La certificazione del design tool...

-

Microchip Technology amplia la partnership con TSMC

Microchip Technology ha annunciato di aver ampliato la sua partnership con TSMC per abilitare una capacità produttiva specializzata a 40 nm presso la sua sussidiaria JASM, nella prefettura di Kumamoto in Giappone. Questa partnership fa parte della...

-

Lauterbach supporta debug e tracciamento per le nuove CPU automotive Arm

Lauterbach ha annunciato il supporto da parte dei suoi strumenti TRACE32 delle CPU Automotive Enhanced (AE) di Arm. Si tratta dei processori di nuova generazione, basati su Armv9, Arm Neoverse-V3AE, Cortex-A720AE, Cortex-A520AE e Cortex-R82AE. Il supporto da...

-

Siemens e Arm: ambiente di simulazione pre-silicio per Arm Cortex-A720 AE

Siemens Digital Industries Software e Arm mostreranno il primo ambiente di simulazione pre-silicio per Arm Cortex-A720 AE per i Software Defined Vehicles (SVD). La nuova soluzione costituisce il primo ambiente di simulazione accelerata in grado di supportare...

-

La nuova soluzione Veloce CS di Siemens per migliorare l’emulazione e la prototipazione

Siemens Digital Industries Software ha presentato Veloce CS, un sistema di verifica e di validazione hardware-assisted che integra all’interno di un unico sistema l’emulazione hardware, la prototipazione di livello enterprise e la prototipazione software. Questa soluzione rappresenta...