ANALOG/MIXED SIGNAL

ELECTRIC VEHICLE

32

- ELETTRONICA OGGI 460 - MARZO 2017

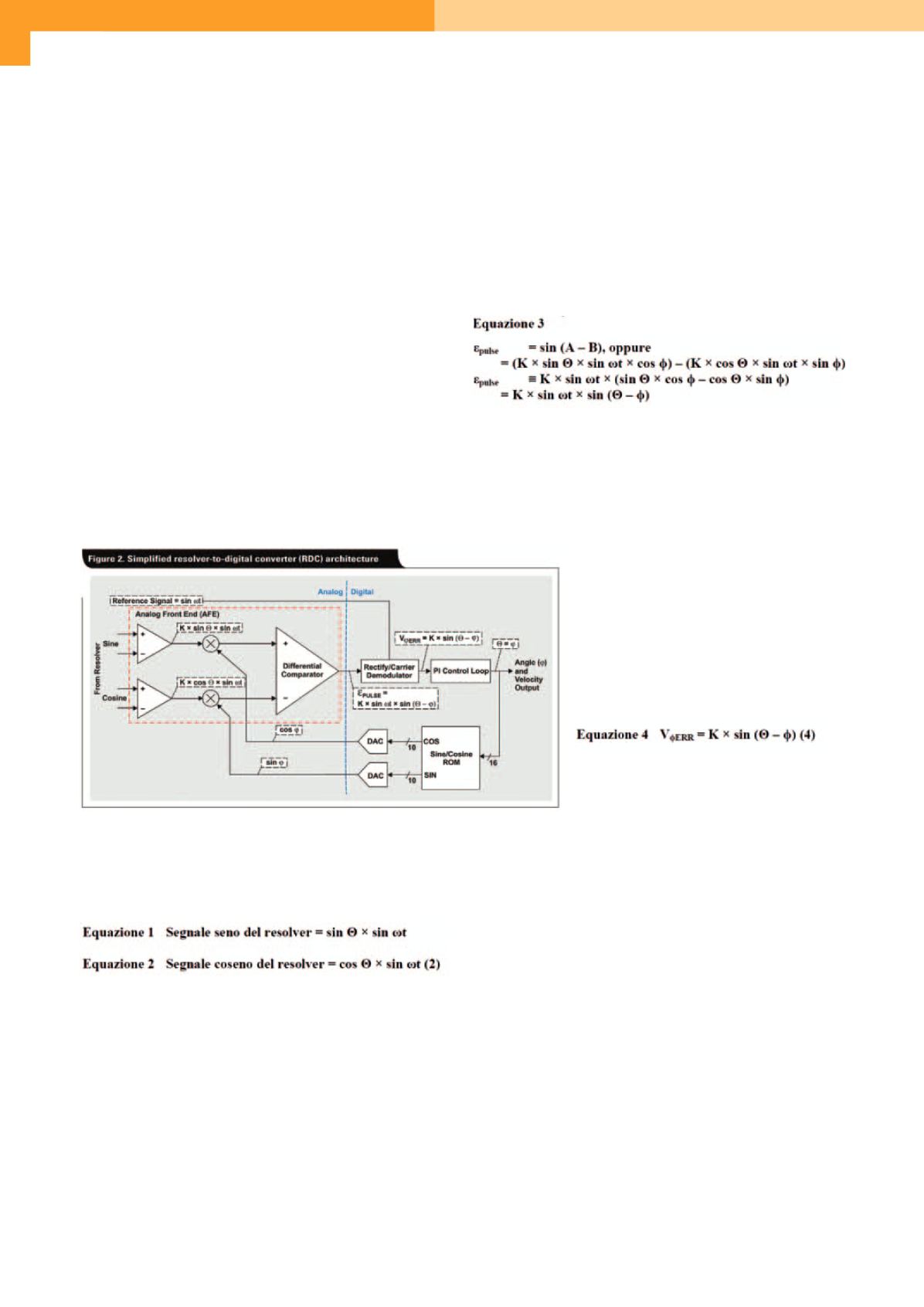

resolver in uscite digitali relativi ad angolo e velocità.

Il front-end analogico (AFE) è formato da amplificato-

ri a guadagno programmabile e da un comparatore. Il

blocco AFE esegue il condizionamento dei segnali di

uscita del resolver eliminando il rumore, impostando

la corretta polarizzazione in DC dell’ingresso e fornen-

do un valore adeguato del guadagno al segnale AC per

consentirne l’utilizzo da parte dei blocchi successivi.

L’elemento fondamentale della conversione RDC è un

anello di retroazione digitale. Si inizia ipotizzando un

angolo digitale, phi. Questo angolo viene elaborato

digitalmente utilizzando le tabelle di ricerca (look-up

table) relative a seno e coseno presenti in memoria. Il

risultato viene a sua volta trasferito ai corrispondenti

convertitori DAC per le componenti seno e coseno. Le

uscite dei DAC vengono moltiplicati per i segnali del

resolver modulati in ampiezza (equazioni 1 e 2), che

sono gli ingressi delle componenti seno e coseno del-

l’RDC.

dove = angolo dell’albero del resolver e = frequen-

za di eccitazione applicata a R1-R2.

L’obiettivo principale dell’architettura RDC è calcolare

l’angolo di rotazione ( ) e la velocità dell’albero del

resolver. Come mostrato in figura 1, l’informazione re-

lativa alla posizione angolare viene ricavata dall’invi-

luppo (picchi di tensione) dei segnali di ingresso seno

e coseno. Per calcolare l’angolo, il seno di viene mol-

tiplicato per un segnale di retroazione (cos ), dove è

l’angolo risultante dalla tabella di ricerca in memoria.

Analogamente, il coseno di viene moltiplicato per il

segnale di retroazione (sin ). Lo scopo di questa mol-

tiplicazione è risolvere la formula generale: (sin A ×

cos B) – (sin B × cos A) per ottenere sen (A – B).

dove è approssimazione dell’angolo del resolver e K

è una costante.

L’uscita del comparatore differenziale, in forma digi-

tale, viene trasferita direttamente ai blocchi digita-

li per eliminare l’onda portante (o la

componente sin t) con un circuito di

rilevamento sincrono. Questo blocco

di rilevamento sincrono utilizza come

riferimento il segnale di retroazio-

ne dell’eccitatore. L’uscita risultante,

V ERR, è inviata al circuito di controllo

digitale di tracciamento (tracking) per

generare l’angolo di uscita desiderato.

La retroazione negativa della configu-

razione dell’anello di controllo utilizza-

ta in questa architettura RDC contribu-

isce a ridurre su base continuativa il

segnale V ERR in modo che risulti mol-

to prossimo allo zero. Per bassi valori di – , V ERR

è quasi zero. Il circuito di retroazione digitale, grazie

alla correzione continua, approssima l’errore a zero in

modo tale che l’angolo di uscita ipotizzato dell’RDC ( )

risulti uguale all’angolo dell’albero del resolver ( ).

Come visibile in figura 2, il segnale V

ERR

viene inviato

all’anello di controllo PI (servo circuito diretto Tipo II).

Sono possibili molte topologie di controllo per l’imple-

mentazione del tracking dell’anello.

Una delle configurazioni di controllo della retroazione

più comuni prevede l’uso di un’azione di tipo integrale.

[3,4]

Il vantaggio di questa configurazione di controllo è

la sua capacità di ridurre praticamente a zero l’errore

di tracking nello stato stazionario. Tuttavia, è necessa-

rio prendere le opportune precauzioni, in quanto un

guadagno leggermente eccessivo relativa all’azione

integrale può causare delle oscillazioni nel sistema o

addirittura instabilità. Questa problematica si risolve

Fig. 2 – Architettura semplificata di un’architettura RDC (Resolver-to-Digital)