42

- ELETTRONICA OGGI 458 - NOVEMBRE/DICEMBRE 2016

DIGITAL

FRAME BUFFER

la visualizzazione di scene ad elevato range dinamico

(la profondità dell’HDR è 64 bit invece di 24). Molte di

queste GPU di fascia alta supportano più display ad

alta definizione, il che implica la presenza di un buffer

interno dedicato per ciascuno di questi display.

Tutte le caratteristiche appena sopra delineate non

sono richieste nella maggior parte dei dispositivi in-

dossabili e portatili a causa delle ridotte dimensioni

dei loro display. L’approccio ideale sarebbe quello

di utilizzare le risorse della memoria integrata della

MCU come frame buffer. Ciò garantisce il più eleva-

to throughput a fronte della massima semplicità di

implementazione. Molte CPU non dispongono di una

memoria di dimensioni sufficiente per supportare i di-

splay di ultima generazione dei dispositivi indossabili.

Senza dimenticare che la crescente complessità dei

programmi richiede che uno spazio sempre maggiore

della memoria integrata sia utilizzata come cache di

primo livello (L1) della MCU.

La maggior parte dei dispositivi indossabili dell’at-

tuale generazione è dotata di display con risoluzione

QVGA (Quarter Video Graphic Array). Per display di

questo tipo le specifiche più comuni sono: 24 bit, riso-

luzione 480 x 360 e velocità di 30 fps. Ciò si traduce

in una densità di pixel (PPI – Pixel Per Inch) pari a 300

per i display dei dispositivi indossabili. I requisiti per

questo tipo di display prevedono una memoria di 4 Mb

con un throughput pari a 120 Mbps. I futuri dispositi-

vi saranno dotati di display con risoluzione molto più

elevata, con densità di pixel di 400 ppi, come molti te-

lefoni cellulari delle ultime generazioni. L’amento della

densità di pixel a parità di dimensioni del display im-

plica un corrispondente incremento delle dimensioni

del frame buffer.

Come già spiegato in precedenza, esistono due mo-

dalità per implementare un frame buffer di queste

dimensioni: un buffer da 4 Mb con un throughput di

120 Mbps o un buffer di 16 Mb con un throughput di

30 Mbps. Tra le due alternative, quella che prevede

un buffer di dimensioni inferiori può vantare molte-

plici benefici: ingombro più ridotto (nel caso

di implementazioni sotto forma di die o Csp),

minor consumo di potenza, costo inferiore e

disponibilità di un maggior numero di opzioni

(a un aumento della densità corrisponde una

diminuzione del numero di costruttori e di

versioni). Nel caso dei dispositivi indossabili,

ingombri, consumi e costo sono i criteri che

determinano la scelta dei componenti di un di-

spositivo.

DRAM vs SRAM

Per le operazioni di frame buffering il tipo di

memoria più usato è la DRAM (Dynamic RAM),

nonostante il fatto che la memoria ad alte pre-

stazioni disponibile su più larga scala attualmente è la

SRAM (Static RAM). Rispetto alle RAM statiche, quelle

dinamiche sono caratterizzate da consumi più elevati

e throughput inferiore. Anche se contraddistinte da

migliori prestazioni, quindi ideali per i dispositivi por-

tatili delle più recenti generazioni, le RAM statiche non

sono usate in un gran numero di prodotti con batteria

di backup. Ciò è dovuta al fatto che l’offerta per questo

tipo di memorie è abbastanza limitata: le SRAM stati-

che sono infatti disponibili in modelli a bassa densità,

fino a 128 MB. La struttura di una cella di memoria di

una RAM statica, che prevede 6 transistor, è più com-

plessa rispetto a quella di una RAM dinamica, formata

da 1 transistor e 1 condensatore. Questo è il motivo

per cui l’implementazione di RAM statiche con densità

più elevate risulta difficile. Nonostante tale limitazione

abbia precluso l’utilizzo di RAM statiche nei dispositi-

vi consumer “legacy” (personal computer, apparecchi

televisivi e telefoni cellulari), esse possono trovare

spazio nei dispositivi indossabili, in considerazione

del fatto che l’operazione di frame buffering richiede

memorie di ridotte dimensioni. Nel caso delle SRAM,

le maggiori prestazioni (un throughput più elevato

corrisponde a minori consumi) rappresentano un in-

dubbio vantaggio.

Considerate quasi estinte, le SRAM sembrano desti-

nate a una seconda giovinezza grazie alla richiesta di

alte prestazioni e, soprattutto, di diminuzione dei con-

sumi da parte dei dispositivi indossabili.

Molti dei principali produttori di memorie RAM sta-

tiche hanno sviluppato una serie di innovazioni per

soddisfare in particola modo le richieste provenienti

dal mercato dei sistemi indossabili – dalla maggiore

affidabilità all’implementazione di nuovi tipi di packa-

ge. Azienda di riferimento nel settore delle SRAM,

Cypress è una protagonista nel mercato dell’Internet

of Things, proponendo una gamma di memorie che

spazia dai modelli che garantiscono la più elevata af-

fidabilità a quelli offerti in package Cps (Chip Scale

Package) di dimensioni miniaturizzate.

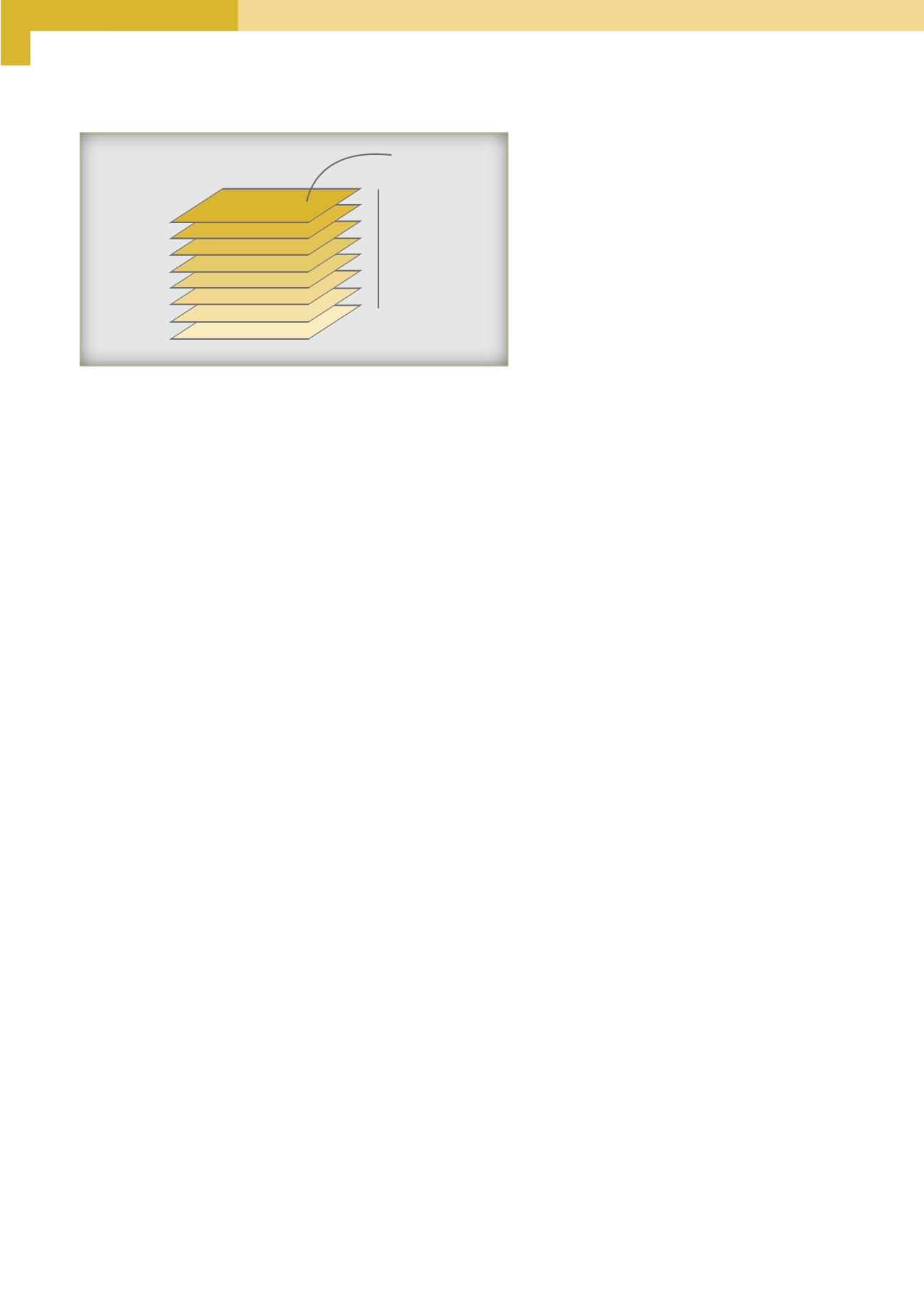

Fig. 2 – In un display a colori a n bit, ciascuno di questi n bit e un piano di bit

separato (Fonte: National Programme on Technology Enhanced Learning, India)

The majority of visually

significant data is

on this plane

As we go down the planes

more subtle details are

added to the image

(MSB) BIT PLANE 7

BIT PLANE 6

BIT PLANE 5

BIT PLANE 4

BIT PLANE 3

BIT PLANE 2

BIT PLANE 1

(LSB) BIT PLANE 0