DIGITAL

SECURITY

39

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

Nel caso il prodotto preposto alla sicurezza evidenzi un erro-

re di natura logica o fisica (guasto di un componente, disturbi

impulsivi dell’alimentazione, picchi di forme d’inda di natura

sconosciuta e così via), esso entra in uno stato di sicurezza.

Ciò garantisce che il prodotto in questione non continuerà a

operare in uno stato difettoso.

Anche i prodotti di rete basati su FPGA possono essere modi-

ficati attraverso una connessione di rete (attacco di tipo front

door). Se vi è un tentativo di modificare il progetto, i mec-

canismi di anti-manomissione o un progetto di tipo “fail-safe”

saranno in grado di rilevarlo e interrompere il funzionamento

del prodotto.

Root of Trust basato su hardware

Gli FPGA e le funzionalità di sicurezza integrate degli attuali

prodotti garantiscono significativi vantaggi in termini di RoT

(Root of Trust) basato su hardware dei sistemi. Esse prevedo-

no memorizzazione di chiavi protette, offuscamento

e tecniche anti-manomissione, oltre a funzionalità

contro la contraffazione e di cifratura asimmetrica

come la funzione PUF (Physically Unclonable Fun-

ction) e gli acceleratori crittografici (Elliptic Curve

Signature) implementati in hardware. Un ulteriore

vantaggio è rappresentato dal supporto della ARM

Trustzone da parte dei sistemi HPS basati su core

ARM A9 e A53.

Un’area di ricerca che riguarda le logiche program-

mabili per le appliance per la sicurezza della rete è

quella dei processori in architettura RISC (Reduced

Instruction Set Computing) personalizzati per funzio-

nalità di sicurezza di reti specifiche implementati su

FPGA. Uno, in particolare, sviluppato dall’università

di Cambridge e denominato CHERI (Capability Har-

dware Enhanced RISC Instructions), prevede MMU

(Memory Management Unit) e interfacce di memo-

ria custom che permettono di affrontare le carenze

più comuni e note dei linguaggi di programmazione

basati su C. Ciò permette ai prodotti predisposti per

la sicurezza basati su logiche programmabili di sce-

gliere architetture di processori “soft” personalizzate

in base al tipo di minacce o alla superficie di attacco

(attack surface, ovvero la parte del sistema che può

essere esposta a un attacco) di un particolare nodo

nell’architettura di sicurezza.

Il punto di vista delle aziende

Numerose aziende, tra cui

Intel

e

Freescale (NXP)

,

hanno partecipato alla definizione del modulo TPM

(Trusted Platform Module), che rappresenta un

esempio di RoT implementato in hardware finalizza-

to al miglioramento della sicurezza delle applicazioni

e del sistema operativo nei sistemi di elaborazione. Intel, dal

canto suo, ha sviluppato la tecnologia TXT (Trusted Execution

Technology) che è ora integrata nelle moderne architetture

di CPU.

I prodotti

ARM

, dal canto loro, non rendono disponibili so-

luzioni RoT basate su hardware, anche se alcuni partener

dell’ecosistema della società forniscono dei framework in

grado di sfruttare i vantaggi di una RoT di tipo hardware.

Nist (National Institute of Standards and Technology)

è

una delle principali organizzazioni, insieme a molte altre,

che si sta occupando della definizione di standard il cui

obbiettivo è trasferire la RoT dal software al firmware, al

firmware per il boot e infine all’hardware per i dispositi-

vi mobili e le tecnologie IoT. La documentazione prodotta

da questi Enti dà per scontato il fatto che le RoT basate

su software sono fonte di problemi e che una soluzione di

tipo firmware è migliore, ma l’integrazione nell’hardware di

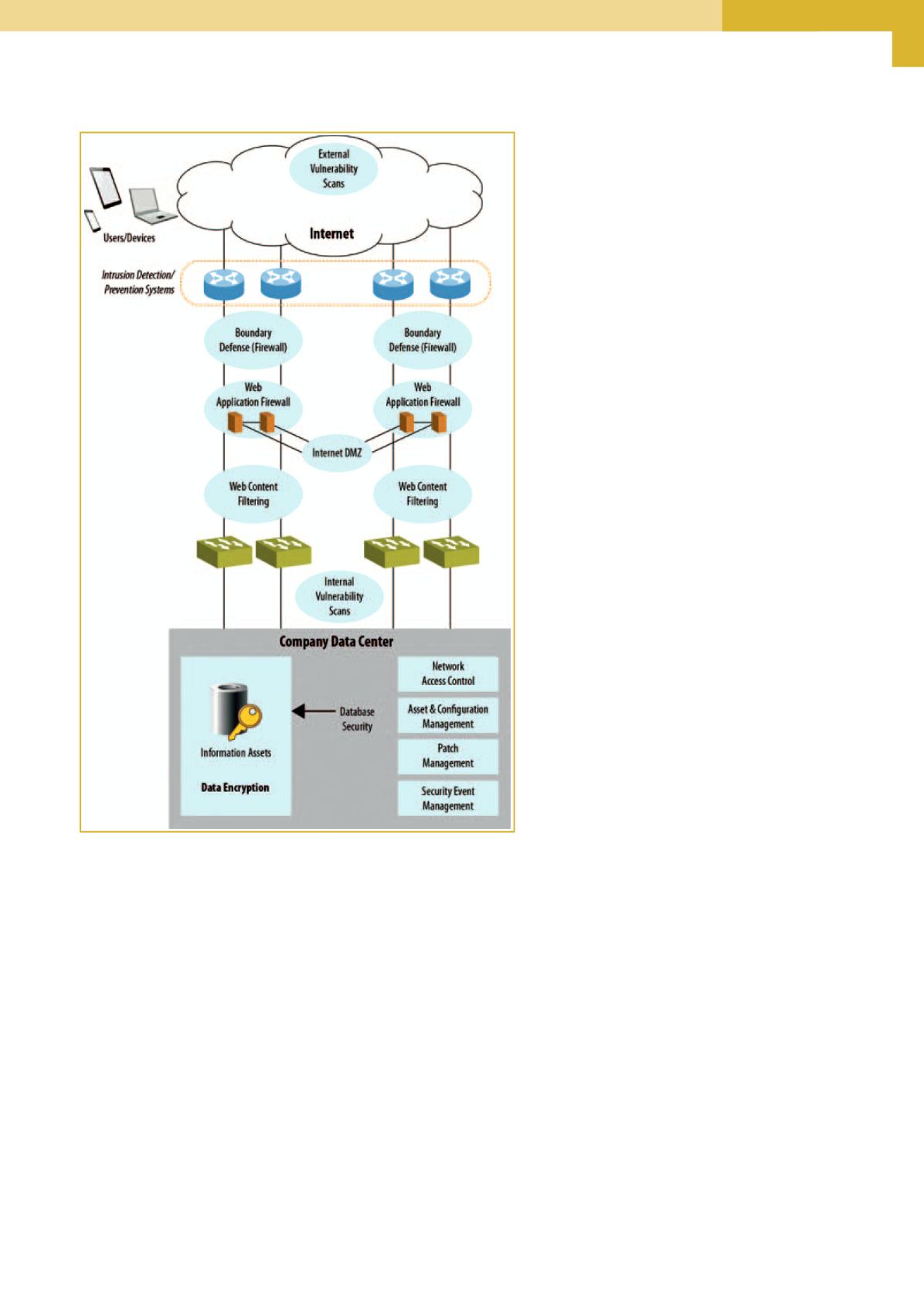

Fig. 1 – Rilevamento delle intrusioni