TECH-FOCUS

NEURAL NETWORKS

36

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

ricerca quadriennale BrainScaleS, terminato a marzo

2015. In questo ambito, laboratori di punta, quale ad

esempio

Imec

, hanno avviato ricerche in questa dire-

zione, aprendo un laboratorio specializzato (NERF).

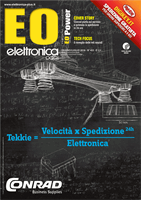

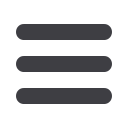

I chip sviluppati nel progetto SpiNNaker sono di tipo

GALS (Globally Asynchronous Locally Synchronous)

e integrano ciascuno 18 nodi realizzati con proces-

sori ARM968 (Fig. 10) collocati in altrettante isole di

tipo sincrono, circondate da un’infrastruttura asin-

crona di intercomunicazione di tipo packet-switched,

affiancata da una

SRAM da 128

MByte collocata

a fianco del chip

multicore, come si

può vedere nella

foto di figura 11.

Fra i vari laborato-

ri attivi in questo

settore, il

MIT

di

Boston ha pro-

gettato un chip

– presentato alla

scorsa ISSCC a

San Francisco e di nome Eyeriss – in grado di im-

plementare una rete neurale che può operare a una

velocità dieci volte superiore a quella di una GPU per

dispositivi mobili. Il chip integra ben 168 CPU con la

propria memoria di lavoro locale, in modo da mini-

mizzare la frequenza con cui i processori debbono

scambiare dati con banchi di memoria centralizzati.

Un approccio di tipo un po’ differente è invece quel-

lo scelto dai laboratori della

Stanford University

,

che hanno optato per una soluzione di tipo misto;

al fine di ottenere una simulazione il più possibile

realistica del modo di operare del cervello, hanno

scelto di affidare a circuiti di tipo analogico il compi-

to di emulare l’attività dei canali a ioni, e a circuiti di

comunicazione di tipo digitale di attuare le intercon-

nessioni sinaitiche.

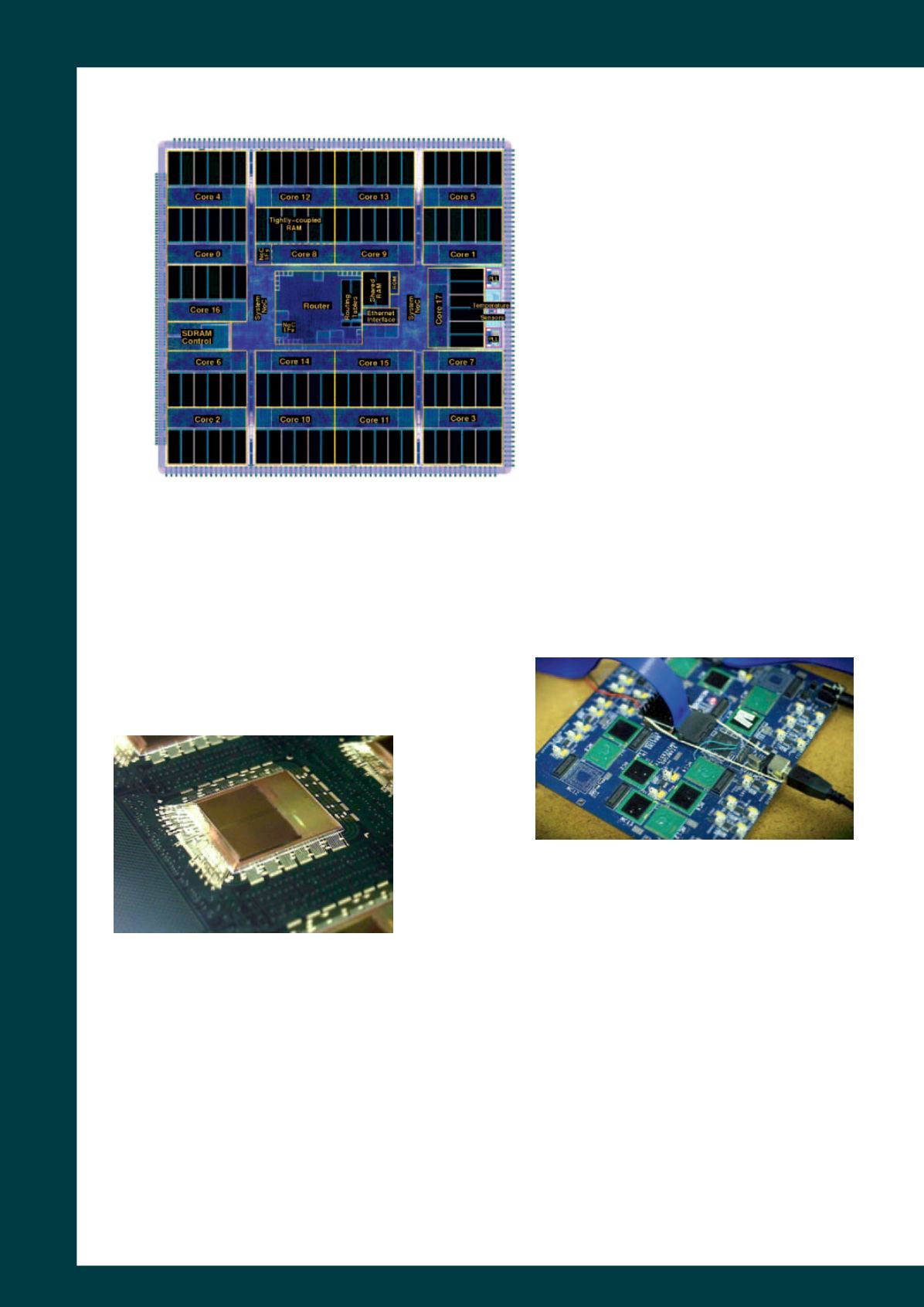

Il tutto è implementato tramite una scheda detta Neu-

rogrid (Fig. 12) che utilizza sedici “neurocore” in gra-

do di emulare il comportamento di oltre un milione di

neuroni connessi da vari miliardi di sinapsi in tem-

po reale, a una velocità novemila volte maggiore di

quella di un supercomputer ma con un assorbimento

estremamente ridotto, solo cinque watt. I chip sono

interconnessi tramite una rete binaria capace di ope-

rare a 80 milioni di spike/sec, utilizzando due tipi di

RAM, una on-chip e una esterna.

Varie sono poi le società che progettano architettu-

re da commercializzare come blocchi di IP. Ne è un

esempio Pneuro Engine dei laboratori francesi

CEA

,

una rete neurale da implementare in strutture qua-

li FPGA e SoC. Si tratta in pratica di un acceleratore

specifico per le reti neurali e l’analisi delle immagini.

Proprio a proposito di FPGA, anche un gigante delle

logiche programmabili quale

Xilinx

si è dimostrata

estremamente interessata al settore delle reti neurali.

Infatti, è di pochi mesi fa la notizia secondo cui Xilinx

ha effettuato un sostanzioso investimento in

TeraDe-

ep

Inc, una società che sviluppa architetture per reti

neurali di tipo convoluzionale come parte del pro-

gramma Data Center Ecosystem.

Citiamo infine un originale progetto che coinvolge

anche un partner italiano, e precisamente l’

univer-

sità di Parma

che, in collaborazione con l’

istituto

Kurchatov

, l’

università di Mosca

, il

MIPT

(Moskow

Institute of Physics and Technology) e l’

università

di San Pietroburgo

ha dimostrato che è possibile

realizzare una rete neurale organica a polianilina in

grado di effettuare operazioni logiche. L’elemento-

chiave in grado di fungere da elemento sinaptico è

un memristore organico.

Fig. 12 – La scheda Neurogrid utilizza sedici “neurocores”,

ed è in grado di emulare il comportamento di oltre un milio-

ne di neuroni connessi da vari miliardi di sinapsi

Fig. 10 – Il die multi-core è affiancato da una SRAM da 128 MB

Fig. 11 – Chip multi-core

a 18 processori SpiNNAKER