NEURAL NETWORKS

TECH-FOCUS

33

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

bilità nella visione e nel riconoscimento automatico

di forme, le cui applicazioni vanno dalla robotica alla

“machine automation”, dal controllo gestuale alla re-

altà aumentata. Il vision-processor Myriad-2 MA2450

VPU è in grado di eseguire ben 2 Teraoperazioni al

secondo consumando solo 500 milliwatt. La capacità

di gestire video viene valutata in 600 Mpixel al se-

condo, con la possibilità di gestire fino a 6 videoca-

mere HD da 1080p60.

È di pochi mesi orsono l’annuncio da parte della ca-

liforniana

BrainChip

di voler collaborare con i chip-

maker nel settore degli smartphone e della IoT, uti-

lizzando il cosiddetto “neuromorphic processing” di

tipo hardware. È stato realizzato un primo processo-

re, con sigla SNAP-64, di cui si intende commercializ-

zare la proprietà intellettuale.

L’architettura SNAP64 consente di controllare fino

a 64 mila neuroni per chip, e i chip possono esse-

re interconnessi fino a ottenere un totale di 256 mi-

liardi di neuroni. Uno dei vantaggi dell’approccio di

BrainChip è quello di utilizzare una memoria distri-

buita nelle sinapsi, ciò che permette di aggiornare

vari milioni di neuroni al secondo. Attualmente, le

sinapsi sono ampie 18 bit, l’integratore nei dendriti

è ampio 22 bit, mentre l’integratore di soma è di 24

bit. L’ampiezza dei vari componenti può comunque

essere configurata per ottenere maggiore o minore

risoluzione.

Il ruolo della ricerca

IBM, fra le tante aree di ricerca, ha avviato alcu-

ni anni fa un progetto di nuovi chip per computer

di tipo “brain-inspired”, basati su di un’architettura

denominata TrueNorth. Si tratta di un processore

“neuromorfico” (Fig. 1) che integra ben un milione

di neuroni configurabili e 256 milioni di sinapsi pro-

grammabili, che fanno capo a 4096 unità neurosinap-

tiche digitali (Fig. 2), supportate da 400 Mbit di RAM.

Il tutto con un consumo di soli 70 milliwatt nonostan-

te i 5.4 miliardi di transistor integrati, con una densità

di potenza di soli 20 mW per centimetro quadrato.

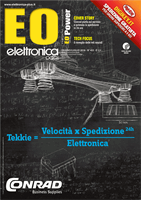

In figura 3 è mostrato il core Neurosynaptic System

4 montato sulla scheda di controllo. L’architettura

interna è di tipo non-von Neumann, distribuita, a ele-

vato parallelismo, priva di clock, scalabile e defect-

tolerant, che ha richiesto lo sviluppo di un CAD appo-

sitamente progettato, in quanto la struttura di questi

chip è drasticamente diversa da quelle classiche, e

integra contemporaneamente circuiti sincroni e asin-

croni. La tecnologia utilizzata è quella di 28 nm, in

collaborazione con

Samsung

.

Lo sforzo realizzato da IBM nella progettazione di

questo chip deriva anche dalla spinta della

DARPA

(l’agenzia di ricerca del dipartimento della difesa

USA), che ha chiesto a IBM di approfondire gli studi

sui chip neurali per l’utilizzo nei sistemi di riconosci-

mento di immagini e del trattamento dati da un ele-

vato numero di sensori in ambiente altamente distur-

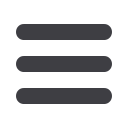

bato. Proprio nell’ambito di questa collaborazione

è stata realizzata la scheda Synapse che utilizza un

array di 16 processori TrueNorth, visibile in figura 4.

In realtà, il progetto del chip TrueNorth è stato svi-

luppato originariamente proprio nell’ambito del pro-

Fig. 3 – Il core Neurosynaptic System 4 di IBMmontato sulla

scheda di controllo

Fig. 4 – La scheda Synapse di IBM, che utilizza un array di

sedici processori neuromorfici TrueNorth

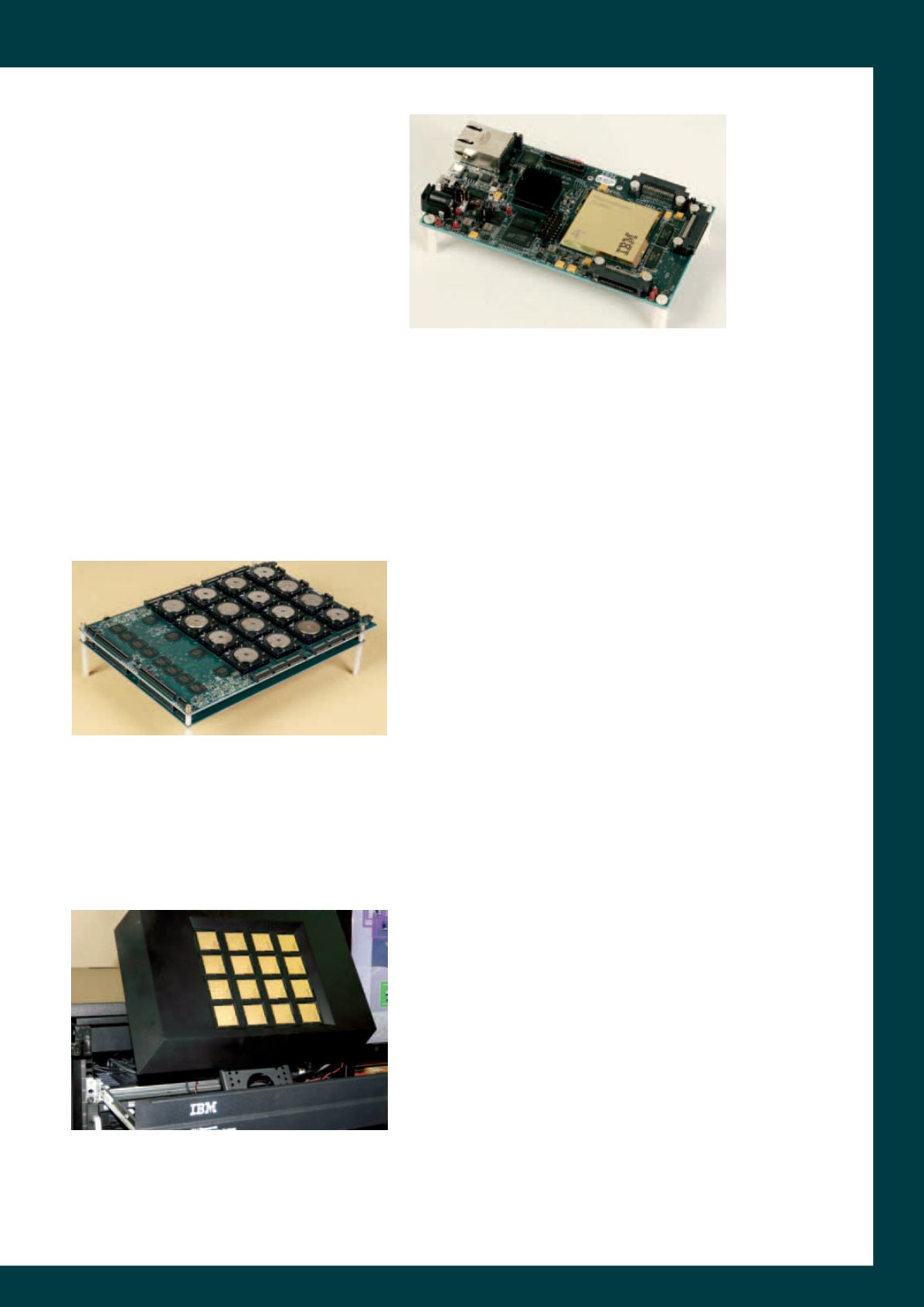

Fig. 5 – Sedici processori neuromorfici TrueNorth di IBM

costituiscono il nucleo del supercomputer da 1 milione

di dollari acquistato dai Lawrence Livermore National

Laboratories