NEURAL NETWORKS

TECH-FOCUS

35

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

Il chip Quark SE di Intel utilizza

una tecnologia messa a punto da

NeuroMem, che fra l’altro dispo-

ne di un proprio core di “Pattern

Matching and Learning Accele-

rator” denominato CM1K. Questo

chip integra 1024 neuroni, basati

su 256 byte di SRAM e da logica

programmabile che confronta il

pattern in entrata con quello di

riferimento, a una velocità di 192

gigaoperazioni al secondo.

Vari ambiti di ricerca

Al di là dei chip specifici, vi sono

varie entità che operano nel

settore delle architetture brain-

inspired, come ad esempio il

gruppo APT dell’

università di

Manchester

, che lavora – assie-

me ad ARM e a molte altre uni-

versità – al progetto SpiNNaker

(Spiking Neural Network Archi-

tecture). L’obiettivo è quello di

realizzare un’architettura di tipo

innovativo, basata su di chip

multi-core realizzati ad hoc.

Queste ricerche vengono realiz-

zate nell’ambito del programma

di ricerca europeo denominato

Human Brain Project, che suc-

cede al precedente progetto di

L

E PIÙ RECENTI NOVITÀ

Alessandro Nobile

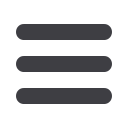

Al recente

CDN Live Cadence

ha introdotto il nuovo Dsp

Tensilica

Vision P6, un di-

spositivo espressamente ideatoper espletare compiti di “visionprocessing” e “depp

learing”, due delle aree applicative più interessanti per le reti neurali.

Nuove istruzioni, maggiore capacità computazionale e altre migliorie stabiliscono

un nuovo standard nei parametri di riferimento delle applicazioni di imaging e di

visione artificiale, aumentando le prestazioni fino a 4 volte rispetto al DSP Tensilica

Vision P5.

Il nuovo Tensilica Vision P6 DSP quadruplica le prestazioni multiply-accumulate

(MAC) disponibili, responsabili di oltre il 95 per cento del carico di lavoro dellamag-

gior parte delle ap-

plicazioni CNN (reti

neurali convoluzio-

nali). Rispetto alle

GPU attualmente

in commercio, in

una tipica imple-

mentazione di rete

neurale il DSP Ten-

silica Vision P6 può

raggiungere delle

velocità di frame

doppie a fronte

di un consumo di

energia molto in-

feriore. Ideale per

una gamma ampia

e diversificata di

funzioni di visione (ad esempio convoluzioni, filtri FIR e moltiplicazione matriciali

e così via), il DSP Tensilica Vision P6 offre prestazioni fino a 4 volte superiori grazie

alle migliorate capacità aritmetiche a 8-bit e 16-bit. Il DSP Tensilica Vision P6 condi-

vide, migliorandola, l’architettura del DSP leader di mercato Vision P5, attualmente

integrato nei processori per applicazioni di telefonia mobile offerti da due dei prin-

cipali fornitori del settore. Compatibile con il DSP Vision P5, il nuovo DSP Vision P6

offre un’unità opzionale in virgola mobile vettoriale SMD a 32-way conforme allo

standard half precision IEEE (FP16). Le prestazioni in virgola mobile raddoppiano

rispetto a quelle della versione Vision P5, facilitando l’utilizzo delle esistenti imple-

mentazioni di reti neurali floating-point.

Il DSP Tensilica Vision P6 può contare su una tool chain di sviluppo completa con

compilatore C ad autovettorizzazione. L’ambiente software garantisce inoltre il to-

tale supportodelle librerie standardOpenCV eOpenVX che, conoltre 1000 funzioni,

permette una rapida migrazione delle applicazioni di imaging/visione esistenti.

Un SDK per reti neurali

Qualcomm

, dal canto suo, ha di recente proposto un Sdk (Software Development

Kit) da utilizzare con i propri processori della linea Snapdragon. Il nuovo Snapdra-

gon Neural procesing Engine supporta le strutture dei modelli di deep learning tra

cui Caffe e CudaConvNet. Obbiettivo di questo SDK è permettere alle aziende ope-

ranti nei più svariati settori – sanitario, automobilistico, della sicurezza e dell’im-

magine – di far girare modelli di reti neurali su dispositivi portatili. Alcuni task di

“deep learning” che possono essere impostati con questo Sdk comprendono il ri-

levamento delle scene, il riconoscimento di testi, la possibilità di rilevare o evitare

oggetti, il riconoscimento del viso e molti altri ancora.

Schema a blocchi del nuovo Dsp Tensilica Vision P6 ottimizzato

per applicazioni nel campo delle reti neurali

Fig. 9 – Il chip Quark SE è utilizzato nei

computer-module open-source Edison