TECH-FOCUS

NEURAL NETWORKS

34

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

gramma DARPA denominato SyNAPSE (che sta per

System of Neuromorphic Adaptive Plastic Electro-

nics) in collaborazione con

Cor-

nell University

.

Sempre nell’ambito di questo pro-

getto, i

Lawrence Livermore Natio-

nal Laboratories

hanno acquistato

un supercomputer da 1 milione di

dollari basato proprio sui chip neu-

romorfici di IBM. Il nucleo di questo

computer utilizza infatti un array di

16 processori TrueNorth, come si

può vedere dalla figura 5. L’attivi-

tà elaborativa di tale computer si

basa quindi su di un totale di 16 mi-

lioni di neuroni connessi da quattro

miliardi di sinapsi.

La stessa Darpa ha investito nel

2013 ben 5.7 milioni di dollari per

lo sviluppo di una “neural grid” da parte dell’universi-

tà del Michigan, con un progetto della durata di quat-

tro anni. L’obiettivo è quello di mettere a punto un’ar-

chitettura hardware e software per realizzare un

processore di immagini ultraveloce, che sia in grado

di processare dati a una velocità di mille volte quella

delle architetture attualmente disponibili. Utilizzando

memristor nelle sinapsi si ottiene una struttura che

non assorbe corrente nel-

lo stato di riposo, garan-

tendo quindi un consumo

di potenza dieci mila volte

inferiore alle soluzioni at-

tuali. I memristor utilizzati

sfruttano la migrazione

di vacanze di ossigeno

nell’ossido di tungsteno

per modulare la trasmis-

sività dei nodi. L’array è

organizzato su tre livelli,

ciascuno dei quali effettua

operazioni di apprendimento successivo delle infor-

mazioni sull’immagine da analizzare.

Approcci differenti

Fra le varie società che hanno avviato ricerche sui

processori di tipo neurale vi sono però interpretazio-

ni differenti.

Intel

, ad esempio, ha annunciato già un

paio di anni fa la propria intenzione di utilizzare archi-

tetture di tipo neurale per i propri processori. Risulta

però che il tipo di approccio sia diverso ad esempio

da IBM, in quanto nei processori Xeon Intel utilizza

un core FPGA in cui integra un software di tipo neu-

rale. Un’altra branca di ricerca

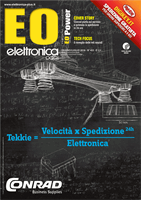

rivelata da Intel utilizza degli LSV

(multi-input Lateral Spin Valves)

e nodi a memristor/PCM (Fig. 6).

Gli LSV si basano di fatto sulla

“spintronica”, in quanto sono dei

micro magneti che cambiano la

loro magnetizzazione in funzio-

ne dello spin degli elettroni che

li attraversano, mentre i memri-

stor variano la loro resistività in

funzione del verso della corrente

che li attraversa, memorizzando

il loro stato in assenza di cor-

rente. Nelle intenzioni di Intel, gli

LSV fungono da neuroni, mentre

i memristori da sinapsi, dove il

valore della resistenza varia in funzione dell’intensità

della corrente e quindi del “peso” del link sinaptico.

Come prima implementazione di tecniche di questo

tipo, Intel ha recentemente lanciato la nuova famiglia

di microcontroller dual-core a 32-bit Quark SE (Fig. 7),

sviluppati specificatamente per le applicazioni di IoT.

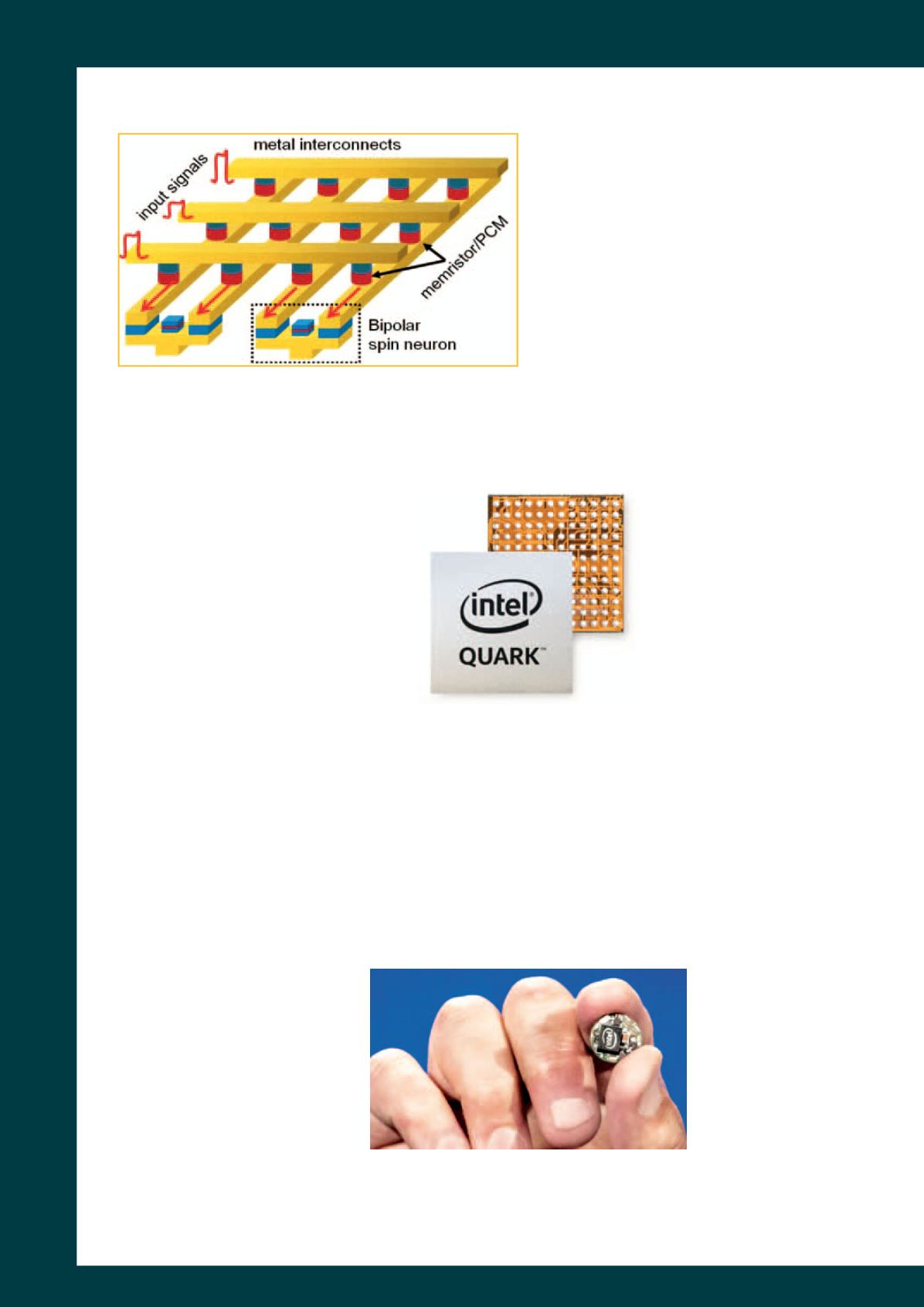

Una prima applicazione è data ad esempio dal piccolo

modulo indossabile Curie (Fig. 8) ottimizzato per il rico-

noscimento dei pattern in

movimento e che integra

un Quark SE, un girosco-

pio e un accelerometro a

6 assi, 384 kB di memoria

flash, 80 kB di RAM e un

modulo Bluetooth.

Un’altra applicazione è

rappresentata dal compu-

ter-module open-source

Edison (Fig. 9) realizzato

in più versioni adattabili a

innumerevoli applicazioni.

Fig. 6 – Nodo neurale di Intel basato su LSV (multi-input

Lateral Spin Valves) e nodi a memristor/PCM

Fig. 7 - Intel ha recentemente lanciato la

nuova famiglia di microcontroller dual-

core a 32-bit Quark SE, sviluppati specifica-

tamente per le applicazioni di IoT

Fig. 8 – Un’applicazione del chip Quark SE è data dal piccolo

modulo indossabile Curie, ottimizzato per il riconoscimen-

to dei pattern in movimento