DIGITAL

BACK-UP MEMORY

42

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

L

e prestazioni di un sistema embedded sono

determinate dalle risorse hardware e software

disponibili. Una parte di un programma scritta in

maniera corretta è in grado di ottimizzare le prestazioni

dell’hardware, sfruttandone al meglio le potenzialità. In

maniera del tutto analoga, un hardware poco efficiente

può penalizzare le prestazioni di un sistema a prescinde-

re dalla bontà del software sviluppato.

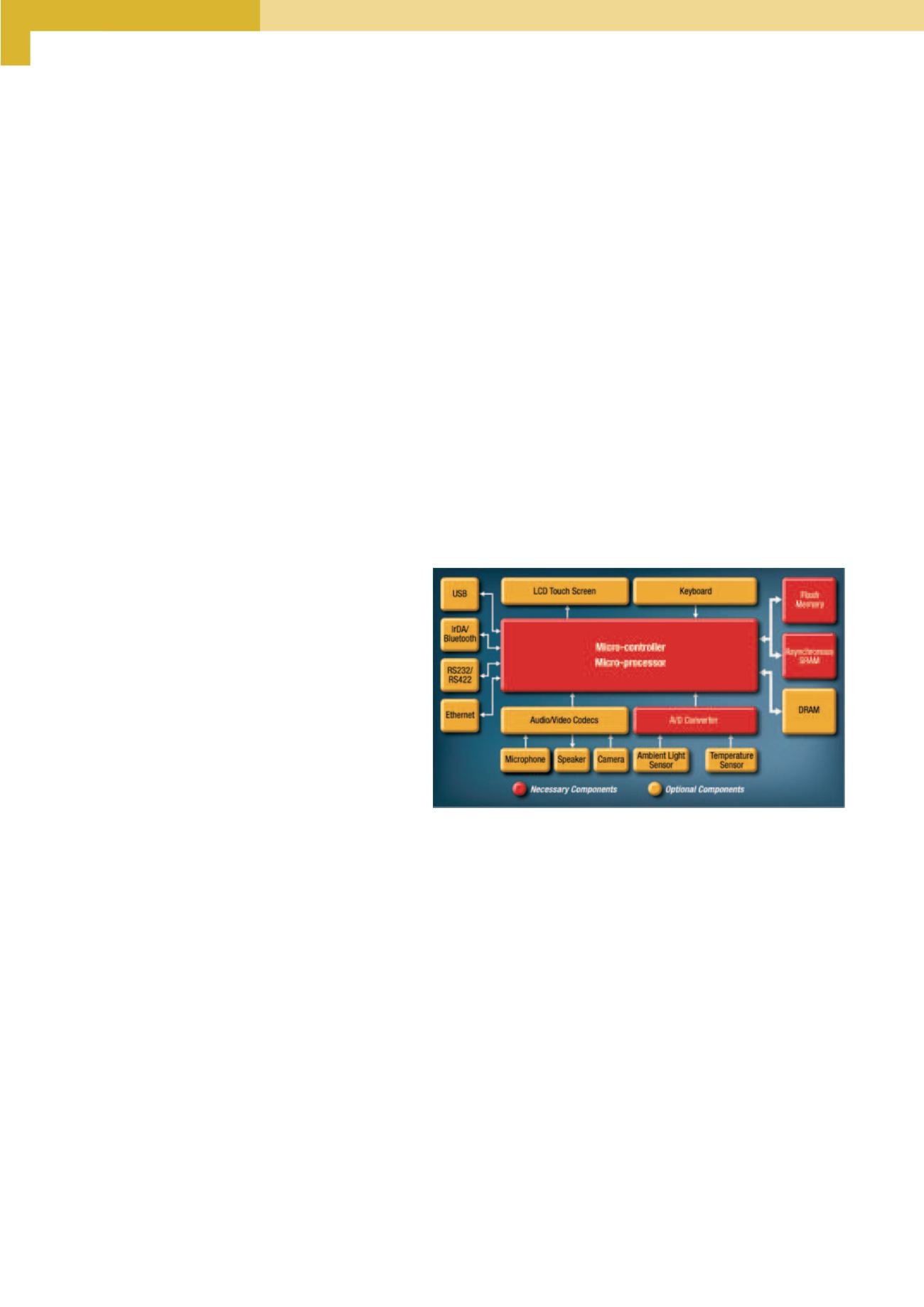

Da parecchi decenni la struttura di un tradizionale siste-

ma embedded non ha subito modifiche. Nella figura 1 è

riportato lo schema a blocchi di un tipico sistema embed-

ded. Il nucleo centrale del sistema è rappresentato da

un microcontrollore o un microprocessore e i progettisti

possono aggiungere o togliere interfacce e periferiche

in base alle necessità. Nel caso la memoria interna del

controllore non sia sufficiente, si ricorre a memorie esterne

come ad esempio flash, SRAM e DRAM.

Prestazioni e budget di potenza sono sempre stati due dei cri-

teri che determinano la scelta dei componenti del sistema, sia

esso il controllore o una qualsiasi delle periferiche. Di conse-

guenza i sistemi embedded si possono classificare nelle se-

guenti tre categorie:

1.

Sistemi “Always ON” (sempre attivi): in questo caso la po-

tenza deve essere fornita da una sorgente continua. Si tratta

di sistemi ad alte prestazioni progettati per funzionare alle più

elevate frequenze operative.

2.

Sistemi alimentati a batteria: una batteria presente a bordo

è la sola sorgente di potenza (come ad esempio nel caso di un

telefono mobile). Anche se le prestazioni sono un parametro

importante, in questo caso la priorità è la durata della batteria.

3.

Sistemi con batteria di back-up (battery backed): questi

sistemi devono essere in grado di funzionare in maniera af-

fidabile anche se viene a mancare l’alimentazione on-board.

Per evitare la perdita di dati critici, i progettisti di sistemi pre-

vedono una piccolo batteria (solitamente del tipo a a bottone

da 240 mAh) per garantire il back-up di funzioni critiche come

la conservazione dei dati nella SRAM e il funzionamento del-

l’RTC (Real Time Un sistema con batteria di back-up sfrutta

l’alimentatore disponibile in condizioni operative normali. In

funzione della mappatura della memoria, esso può eseguire

il codice contenuto nella flash e memorizzare i risultati nella

SRAM. Un aspetto critico è la memorizzazione di questi dati

quando si verificano cadute di alimentazione. La memoria

SRAM è collegata a una batteria alternative presente a bor-

do. Durante il funzionamento normale, l’alimentatore a bordo

fornisce potenza al sistema, mentre quando viene a mancare

l’alimentazione un chip di supervisione commuterà l’alimenta-

zione della SRAM sulla batteria a bordo della scheda ponen-

dola in modalità stand-by.

In un sistema con batteria di back-up, un tipico modello di uti-

lizzo della potenza è riportato in figura 2. Il chip di supervisione

Utilizzo di SRAM veloci

per progetti con memorie

dotate di batterie di back-up

Vinay Manikkoth

Nilesh Badodekar

Cypress Semiconductor

Il basso assorbimento di corrente in modalità “deep

sleep” delle SRAM veloci a basso consumo ne fanno

la soluzione ideale per applicazioni che ricorrono a

una batteria di back up in presenza

di cadute di alimentazione

Fig. 1 – Schema a blocchi di un tipico sistema embedded