DIGITAL

BACK-UP MEMORY

44

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

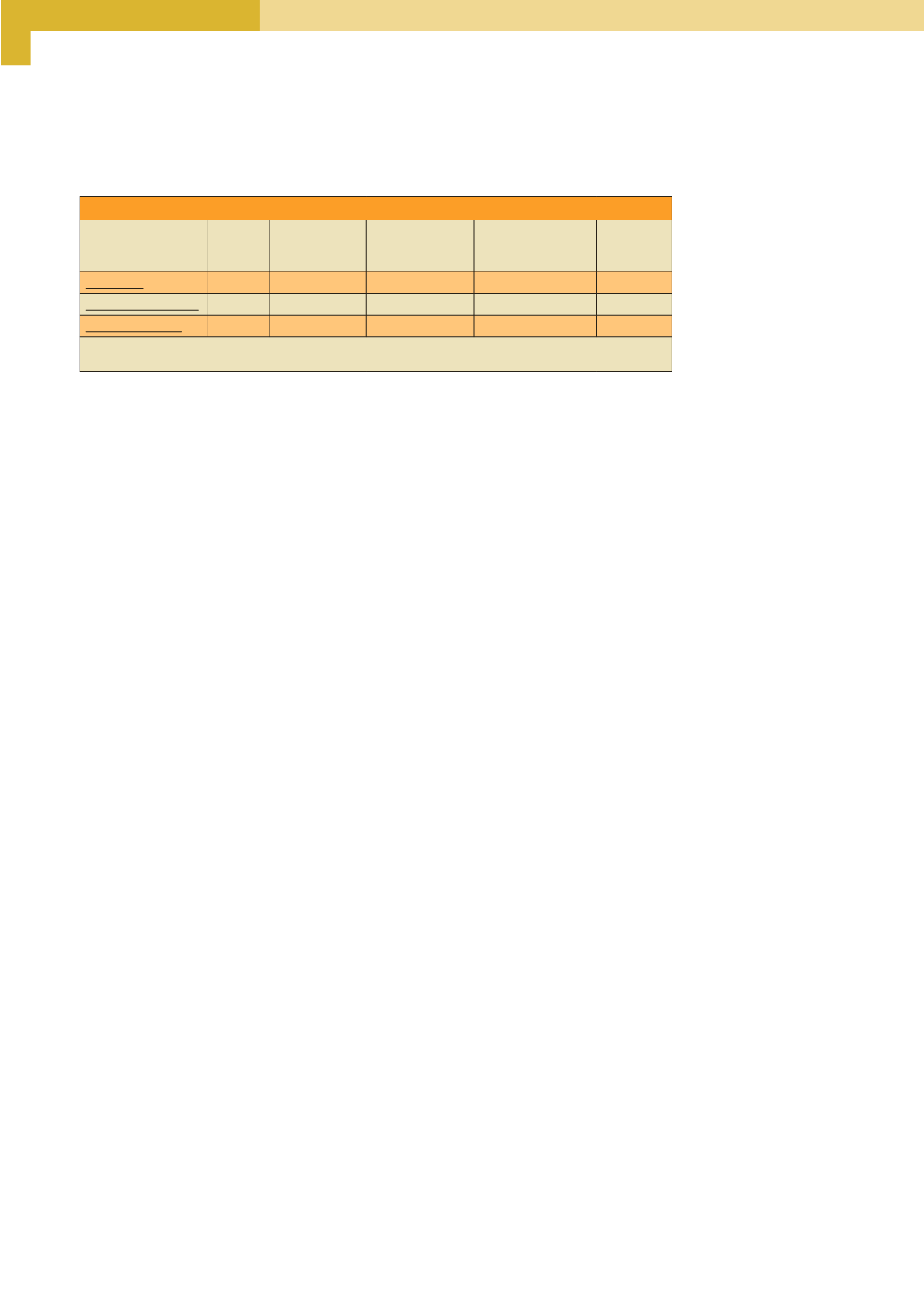

da un segnale di ingresso aggiuntivo che, una volta attivato,

porta il dispositivo in modalità “deep-sleep”. Una SRAM Po-

werSnooze di Cypress, per esempio, è caratterizzata da tem-

pi di accesso di 10 ns, nettamente inferiori rispetto a quelli

di una SRAM a basso consumo, compresi tra 45 e 55 ns. La

corrente assorbita in modalità “deep-sleep” varia da 10 a 20

uA, valori nettamente inferiori rispetto ai 30-40 mA consumati

in stand by da una SRAM veloce da 16 Mb. Nella tabella 1 è

riportato un confronto tra i principali parametri – velocità e

consumo di corrente – delle tre tipologie di memorie SRAM

prese in considerazione.

I progettisti di sistemi possono controllare l’ingresso nella

modalità “deep-sleep” attraverso un GPIO oppure monito-

rando la commutazione in maniera automatica utilizzando il

chip di supervisione. Nel caso di controllo mediante GPIO il

software può utilizzare la modalità “deep-sleep” della SRAM

analizzando gli accessi alla memoria stessa.

SRAM a basso consumo con batteria di back up

La necessità di un circuito aggiuntivo per le memorie con bat-

terie di backup deriva dal fatto che durante una caduta dell’a-

limentazione i controllori non sono più in grado di pilotare i

loro I/O. Sulle linee di segnale saranno quindi presenti livelli

logici intermedi che gradualmente andranno a un livello di

tensione basso (LOW) a causa delle perdite e della capacità

della scheda. La perdita di controllo significa che, anche se

la SRAM è alimentata dalla batteria, il segnale di “chip ena-

ble” andrà a livello logico basso, abilitando di conseguenza

la SRAM. Per evitare il verificarsi di questa eventualità, i pro-

gettisti impiegano un chip di supervisione per monitorare l’a-

limentatore della scheda e controllare il segnale di “chip ena-

ble” della SRAM. Nella figura 3 viene rappresentato lo schema

di un circuito di una SRAM a basso consumo che prevede

l’uso di un chip di superivisione. Tutti le linee dei dati e degli

indirizzi e i segnali di controllo sono pilotati dal processore.

Il segnale di chip enable attivo basso della SRAM è pilota-

to dal chip di supervisione che è pilotato dal segnale di chip

enable del microcontrollore. Nel caso di caduta dell’alimenta-

zione, il chip di supervisione assume il controllo del segnale

di “chip enable” della SRAM pilotandolo al livello logico alto e

ignorando il segnale di “chip enable” del controllore. Il chip di

supervisione effettua la commutazione dall’alimentatore del-

la scheda all’alimentatore

della batteria e disabilita

la SRAM, impedendo in tal

modo la perdita dei dati. Il

secondo segnale di “chip

enable”, essendo un se-

gnale attivo alto, è pilotato

direttamente dal control-

lore mediante un resistore

di pull down “debole” (la cui resistenza non ha un valore ele-

vato). Quest’ultimo garantisce che durante la caduta dell’ali-

mentazione il secondo segnale di “chip enable” viene portato

al livello logico basso disabilitando la SRAM.

SRAM veloci a basso consumo per applicazioni

con batteria di back-up

Il basso assorbimento di corrente in modalità “deep sleep”

delle SRAM veloci a basso consumo ne fanno la soluzione

ideale per applicazioni che ricorrono a una batteria di back

up in presenza di cadute di alimentazione. Durante il funzio-

namento normale la SRAM può essere fatta funzionare ad alta

velocità mentre in caso di caduta dell’alimentazione la SRAM

può commutare automaticamente in modalità “deep sleep”

commutando il segnale “deep sleep” nello stato logico basso.

La figura 4 illustra l’utilizzo di una SRAM che prevede la mo-

dalità “deep sleep”: come si può osservare non è necessario

apportare modifiche a un progetto esistente che fa ricorso a

una SRAM a basso consumo. Quando si verifica una caduta

dell’alimentazione, il chip di supervisione disabilità la SRAM

mentre il resistore di pull-down sul pin “deep sleep” porterà

automaticamente il segnale nello stato logico basso, consen-

tendo così alla memoria di entrare in modalità “deep sleep”. Il

chip di supervisione assicura che la SRAM rimanga disabili-

tata per tutte il periodo in cui l’alimentazione della scheda è

assente. Nel momento in cui viene ripristinata l’alimentazione,

il chip di supervisione continua a mantenere la SRAM disabi-

litata per tutto il periodo di timeout della funzione POR (Power

On Reset) del chip di supervisione.

Questo periodo di timeout può variare da 1 a 100 ms in fun-

zione del tipo di chip di supervisione utilizzato. Il periodo di

timeout consente la ripresa del funzionamento del controllo-

re che può quindi iniziare a controllare il segnale di “deep

sleep” e pilotarlo al livello logico alto. Ciò permette di tener

conto della sequenza di temporizzazione di uscita dallo sta-

to di “deep sleep” di una SRAM veloce a basso consumo e

consente ad essa di predisporsi per l’accesso da parte del

controllore. Le memorie SRAM veloci a basso consumo sono

caratterizzate da tempi di back-up equivalenti a quelli delle

tradizionali SRAM a basso consumo e garantiscono I miglio-

ramenti delle prestazioni richiesti dai progettisti di sistemi

grazie alla riduzione dei tempi di accesso alle SRAM stesse.

Tabella 1 – Confronto tra i principali parametri delle diverse tipologie di memoria SRAM

Tipologia di SRAM

Tempo

di accesso

Corrente

inmodalità attiva

ICC (max)

Corrente

inmodalità standby

ISB2 (tip.)

Corrente

inmodalità Deep-Sleep

IDS (tip.)

Durata

della batteria

++

SRAM veloci

10 ns

110 mA

20 mA

-

24 ore

SRAM a basso consumo

45 ns

36 mA

5,5 µA

-

>3 anni

SRAM PowerSnooze

10 ns

110 mA

20 mA

8 µA

>3 anni**

++: La durata della batteria è calcolata considerando una batteria a bottone da 240 mAH e consumo di corrente in standby tipico

**: La durata della batteria per la SRAM PowerSnooze è calcolata considerando il consumo tipico di corrente in modalità Deep-sleep