DIGITAL

BACK-UP MEMORY

43

- ELETTRONICA OGGI 455 - GIUGNO/LUGLIO 2016

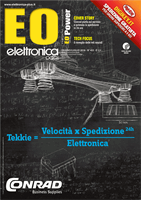

instrada l’alimentazione della scheda durante il funzionamen-

to normale. In presenza di cadute dell’alimentazione, la SRAM

viene commutata verso la batteria e disabilitata dal medesimo

chip. Essa resta in questa modalità fino all’esaurimento del-

la carica della batteria. Una volta ripristinata l’alimentazione

della scheda, il chip di supervisione riprenderà gradualmente

a far alimentare la SRAM mediante l’alimentatore della

scheda. Per completare questa operazione il chip richie-

de un intervallo di tempo compreso tra 1 e 10 ms.

Nel momento in cui sistemi di questo tipo vengono instal-

lati sul campo, la loro manutenzione risulta difficoltosa, in

quanto sono solitamente progettati per non richiedere in-

terventi di manutenzione per un periodo anche superio-

re ai due anni; da qui si evince l’importanza della durata

della batteria. I progettisti di sistemi tendono a scegliere

memorie SRAM che consumano la minor quantità possi-

bile di corrente in modalità stand-by. Tenendo conto del

fatto che è necessario assicurare una lunga durata della

batteria, la scelta di una SRAM veloce è praticamente im-

proponibile. Una batteria a bottone da 240 mAh abbinata

a una SRAM veloce da 16 Mb sarà caratterizzata da una

durata di 12 ore, contro gli oltre 3 anni garantiti da una

SRAM a basso consumo.

I produttori di microcontrollori hanno sviluppato control-

lori in grado di operare a velocità superiori a 150 MHz.

Questi controller integrano modalità a basso consumo

e/o modalità “deep sleep” che assicurano una più elevata

velocità di esecuzione e bassi consumi nel momento in

cui il sistema deve ricorrere alla batteria di back-up.

Un controllore più veloce da solo non è in grado di assi-

curare un miglioramento delle prestazioni se le periferi-

che non sono in grado di adattarsi alla sua velocità. L’in-

terfaccia verso la memoria esterna è una delle principali

connessioni ad alta velocità e una memoria SRAM o flash

a basse prestazioni può diventare un vero e proprio “col-

lo di bottiglia”. L’introduzione di varie modalità – Page,

Burst, XIP (eXecute In Place) – ha permesso di aumentare

il tempo di accesso in lettura di un fattore pari a tre nel

caso delle memorie flash. Ciò significa che un controllore

può effettuare una lettura in una flash in un tempo com-

preso tra 20 e 30 ns (ovvero da 2 a 3 cicli di clock per un

controllore operante a 150 MHz). Nel caso si scelga una

SRAM a basso consumo, il tempo di accesso alla SRAM

sarà compreso tra 45 e 70 ns (che equivale a un numero

di cicli di clock variabile da 4 a 10).

La velocità, un parametro critico

Un progettista può optare per una SRAM veloce (con

tempo di accesso di 10 ns) per aumentare le prestazioni

del sistema, penalizzando quindi la durata della batteria,

oppure scegliere una SRAM a basso consumo a discapi-

to delle prestazioni del sistema stesso.

I produttori di memorie hanno compreso la necessità di rea-

lizzare memorie SRAM che abbinino velocità a bassi consumi.

Oltre alle tradizionali modalità operative – attiva e in standby

– queste memorie prevedono un’ulteriore modalità a basso

consumo denominata “deep-sleep”. Tale modalità è controllata

Fig. 2 – Schema del consumo di potenza di un sistema con batteria

di back up

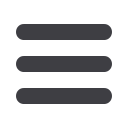

Fig. 3 – Schema di una memoria SRAM a basso consumo con batteria di back-up

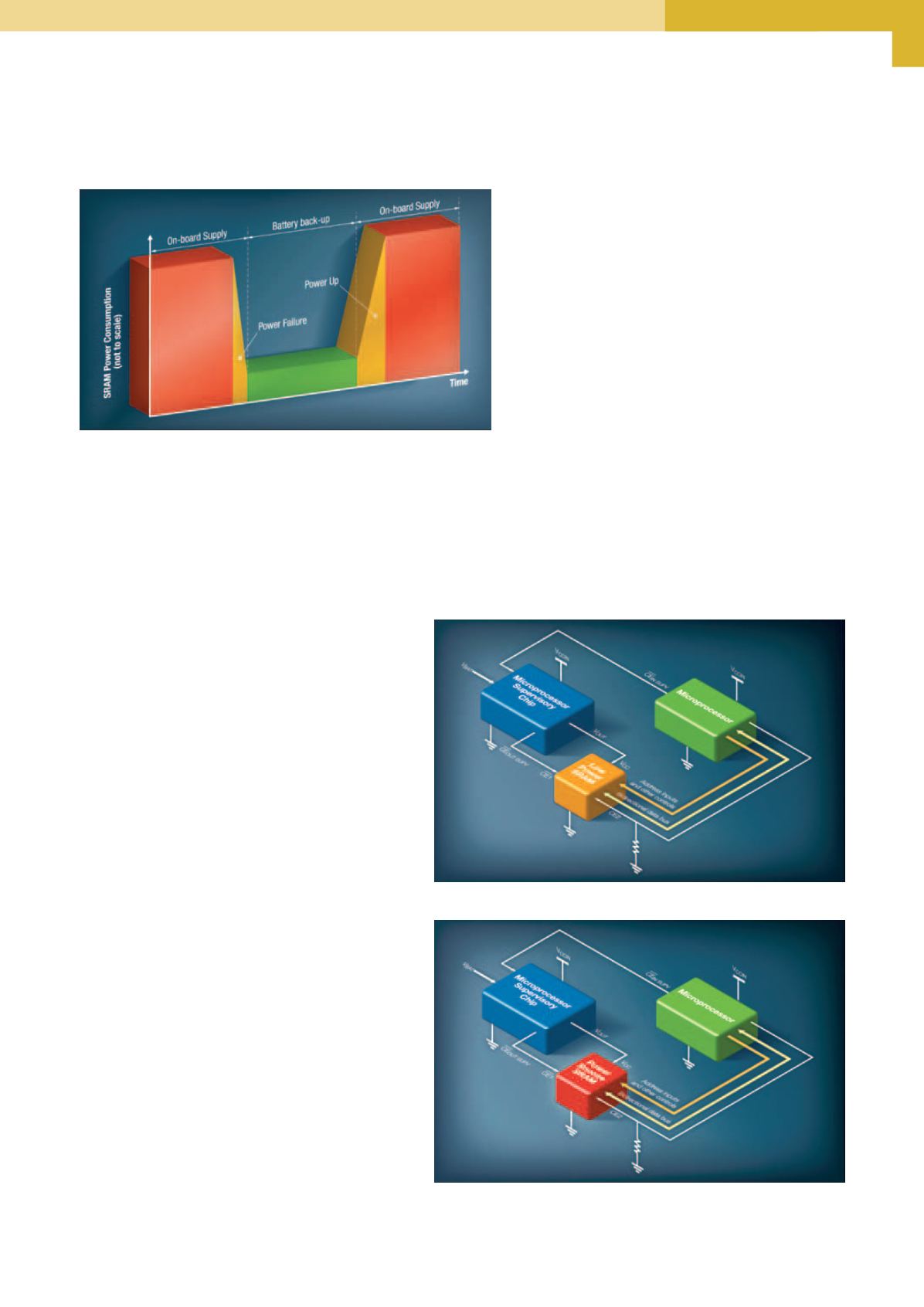

Fig. 4 – SRAM veloce a basso consumo per applicazioni con batterie di back-up