DIGITAL

FPGA

45

- ELETTRONICA OGGI 446 - GIUGNO 2015

ad esempio, include funzioni di tipo

hardened (ovvero implementate in

hardware) quali porte I²C e SPI, tem-

porizzatori e contatori, per fornire

funzioni simili a quelle presenti sui

microcontrollori standard, pur ga-

rantendo una flessibilità molto mag-

giore grazie alle risorse logiche non

dedicate disponibili nel resto della

matrice.

I SoC SmartFusion di Microsemi

sono un esempio di FPGA ibridi

a segnali misti che abbinano una

struttura FPGA, un sotto-sistema

microcontrollore basato su core

ARM Cortex-M3 e un engine di ela-

borazione analogico (ACE – Analog

Compute Engine). L’architettura ibri-

da consente agli sviluppatori di far

girare il software sul core ARM sup-

portato da periferiche personalizza-

te che sono caricate nella struttura

FPGA. L’architettura SmartFusion

prevede anche un controllore di I/O

“intelligente” che ottimizza le presta-

zioni di applicazioni che prevedono

l’impiego di sensori. I blocchi I/O

analogici integrati, sotto il controllo dell’ACE, esonerano il

processore dalla gestione dell’esecuzione in parallelo delle

operazioni. L’engine ACE svolge un ruolo critico in appli-

cazioni quali il controllo di motori che richiedono letture

accurate e tempestive della posizione per assicurare un ag-

giornamento preciso delle uscite che controllano i circuiti

elettronici di potenza.

Elaborazione del segnale

Con l’aumento delle applicazioni di elaborazione del se-

gnale che richiedono l’uso di FPGA, i produttori hanno co-

minciato a aggiungere blocchi “hardened” basati su porte

logiche ASIC per effettuare calcoli aritmetici ad alta veloci-

tà. Il modo più efficace per implementare la moltiplicazio-

ne nelle celle programmabili prevede l’uso dell’aritmetica

seriale. Si tratta comunque di un approccio molto lento,

che offre benefici solo se è possibile eseguire molte ope-

razioni aritmetiche in parallelo.

Il primo passo per superare questo problema è stato l’ag-

giunta di una logica di tipo “carry-chain” (per propagare

i riporti) dedicata, che risulta comunque costosa da im-

plementare nella struttura dell’FPGA. Ciò ha comunque

permesso l’uso di sommatori “carry-lookahead” e “carry-

save” più veloci che consentono l’implementazione di mol-

tiplicatori più veloci. Il passo successivo è stato quello di

fornire blocchi moltiplicatori completi in logica cablata.

Questi blocchi sono stati ottimizzati al fine di ridurre gli

ingombri a bordo del die e possono essere collegati tra di

loro in modo da dar vita a moltiplicatori a 32 e 64 bit più

sofisticati utilizzando la struttura dell’ FPGA per aggiun-

gere funzionalità più sofisticate, come l’aritmetica virgola

mobile.

Alcuni FPGA mettono a disposizione una vasta gamma

di core DSP per soddisfare i requisiti di specifiche appli-

cazioni: le unità a 9 bit sono ideali per l’elaborazione di

immagini e video e mentre quelle che operano su un nu-

mero maggiore di bit sono preferite per l’elaborazione dei

segnali usati nelle applicazioni di comunicazioni e audio.

I blocchi DSP sono apparsi la prima volta nei dispositivi

di fascia alta di produttori come Altera e Xilinx, ma ora si

trovano anche in architetture ottimizzate in termini di costi

come ad esempio quelle delle famiglie Cyclone V e Spar-

tan-6. Per le applicazioni, come la crittografia o operazioni

video specializzate, può essere più indicata un’architettu-

ra dove il rapporto tra logica programmabile e DSP è più

elevato.

n

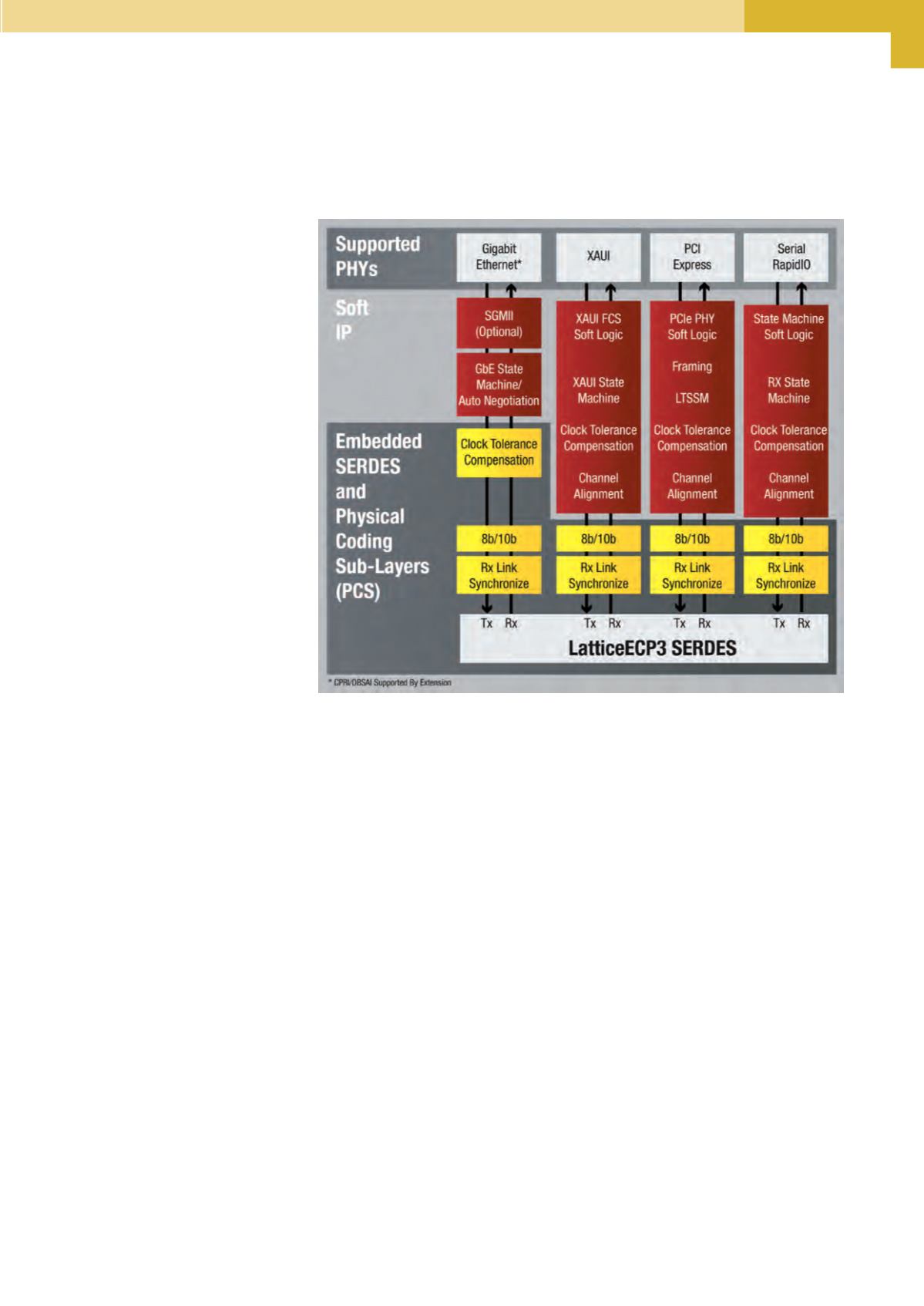

Fig. 4 – Il blocco SerDes è ora integrato nell’architettura di molti FPGA