DIGITAL

FPGA

43

- ELETTRONICA OGGI 446 - GIUGNO 2015

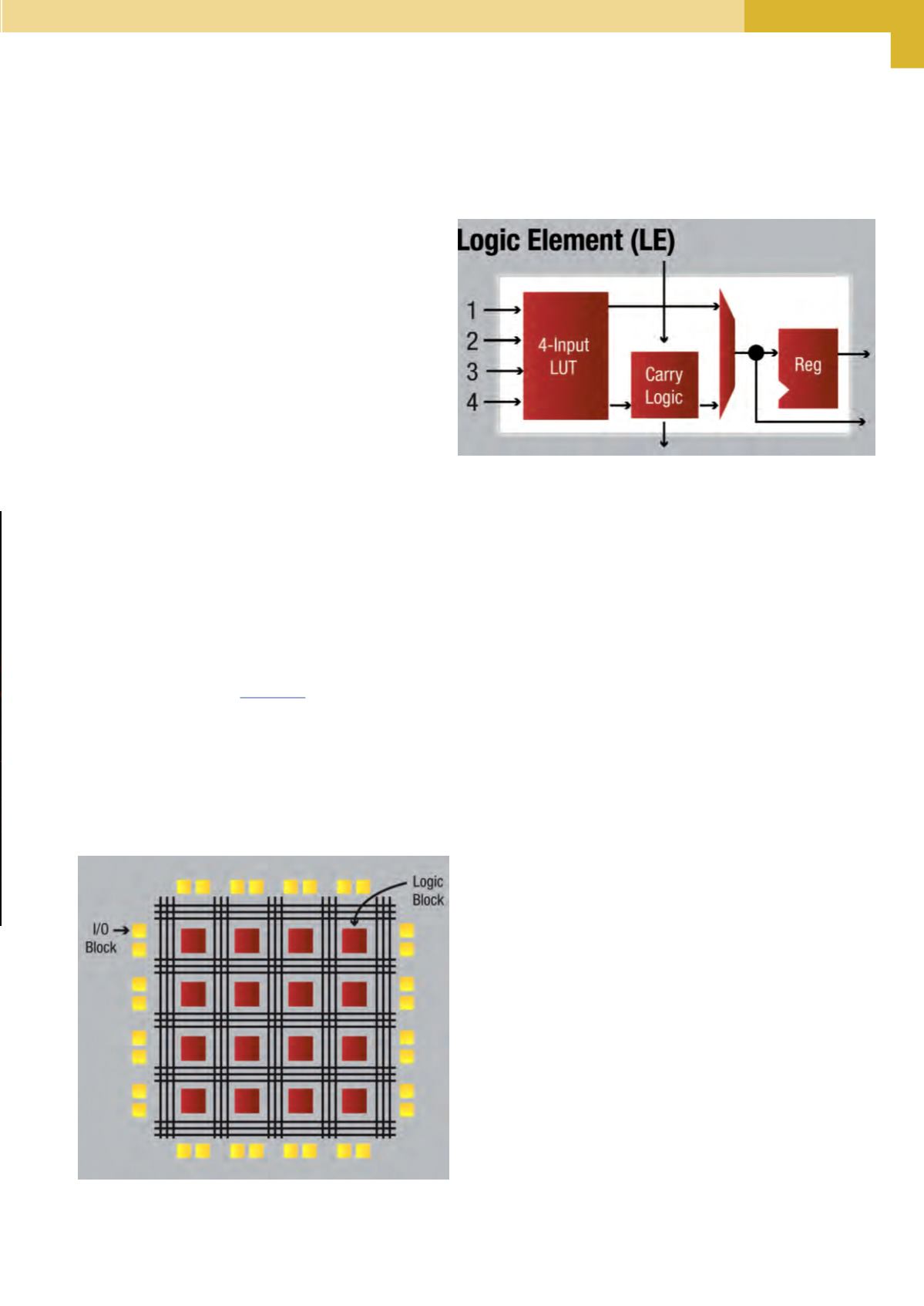

per aggiornare porzioni dell’FPGA mentre il resto del siste-

ma continua a funzionare o per ottimizzare l’uso delle celle

logiche programmabili all’interno della struttura dell’FPGA

(lo schema semplificato è riportato in Fig. 2).

La riconfigurazione parziale è stata ampiamente utilizza-

ta per l’elaborazione di segnali audio e video in quanto

consente la sincronizzazione tra gli algoritmi accelerati in

hardware e il flusso di dati in ingresso. Un dispositivo di

dimensioni inferiori può dunque essere utilizzato per sup-

portare tutti i task richiesti dal sistema mediante la ricon-

figurazione dei circuiti modulari situati all’interno di una

determinata area della struttura dell’ FPGA. Se la riconfigu-

razione parziale non fosse utilizzata, ogni circuito avrebbe

bisogno di essere caricato in parallelo in un dispositivo i

a configurazione fissa di maggiori dimensioni richiedendo

un maggior numero di risorse della struttura dell’FPGA.

FPGA in tecnologia anti-fusibile

Non tutti gli FPGA utilizzano la memoria volatile per la con-

figurazione. I primi dispositivi non volatili erano basati sul-

la tecnologia “anti-fusibile” – un elemento programmabile

una sola volta che forma una connessione quando il fusi-

bile viene ‘bruciato’ elettronicamente da un programmato-

re esterno. Realizzati da

Microsemi, gli FPGA anti-fusibile

sono caratterizzati da una maggiore immunità intrinseca

alle radiazioni ad alta energia rispetto ai dispositivi basati

su memoria, dato che il collegamento permanente forma-

to dall’anti-fusibile non può essere alterato da fenomeni di

SEU (Single Event Upset – impatto di una particella ioniz-

zante su un circuito elettronico che può provocare un impul-

so cambiando la forma dei segnali analogici o lo stato dei

circuiti digitali). Microsemi propone un’opzione non volatile

riprogrammabile negli FPGA delle famiglie SmartFusion,

ProAsic3 e Igloo. Questi dispositivi abbinano un’architettu-

ra basata su LUT con celle di configurazione basate su me-

morie flash. In questo modo l’intero sistema può riavviarsi

istantaneamente dopo uno spegnimento perché la struttura

dell’FPGA conserva il suo stato di configurazione. Tra gli

altri vantaggi da segnalare l’eliminazione della corrente di

spunto in fase di configurazione e il risparmio energetico

ottenibile in presenza di una fonte di alimentazione del di-

spositivo viene spenta e riaccesa. A differenza della tec-

nologia anti-fusibile, le celle di memoria flash sono anche

riprogrammabili. Nel caso di un errore in fase di sviluppo o

di aggiornamento del sistema sul campo, la configurazione

hardware dei dispositivi può essere alterata.

La memoria flash

I dispositivi delle famiglie Igloo, ProAsic3 e SmartFusion di

Microsemi sfruttano la tecnologia di memoria flash per ga-

rantire un funzionamento a basso consumo. La tecnologia

Flash*Freeze degli FPGa della serie Igloo permette di porre

il dispositivo in uno stato di bassissimo consumo quando

non è in uso, memorizzando i dati normalmente conserva-

ti nei registri volatili e negli array della SRAM in un’area

di backup della memoria flash. Una volta memorizzati, il

dispositivo Igloo non necessita più di alcuna corrente per

conservare lo stato delle memorie volatili. Togliendo l’e-

nergia a questi elementi e agli I/O, il consumo può essere

inferiore a 5 µW.

Grazie alle memorie flash è stato possibile sviluppare ar-

chitetture ibride e integrare funzioni di protezione avanzate.

I dispositivi della linea Mach XO2 di Lattice, ad esempio,

prevedono una memoria flash on-chip (Fig. 3) per i dati di

configurazione, in modo da ridurre il rischio di eventua-

li intrusioni da parte di hacker, finalizzate al recupero del

flusso di bit di configurazione durante l’accensione. In

Fig. 1 – Esempio di un elemento logico di un FPGA

Fig. 2 – Struttura semplificata di un FPGA