DIGITAL

FPGA

44

- ELETTRONICA OGGI 446 - GIUGNO 2015

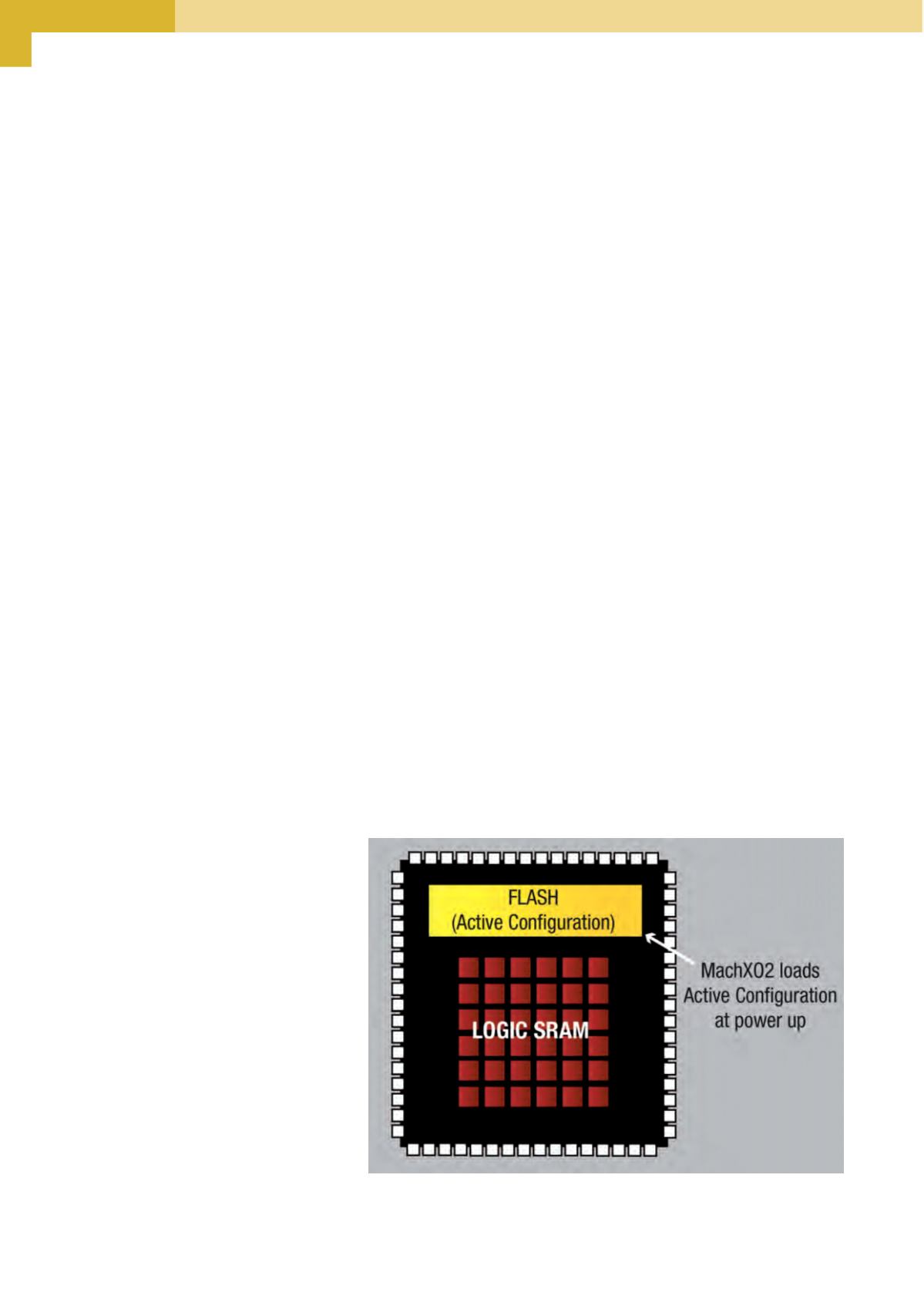

questo modo è possibile eliminare il ricorso a una PROM di

configurazione esterna. I contenuti della flash dei dispositivi

XO2 possono essere caricati nella SRAM attraverso un bus

interno di ampie dimensioni che garantisce l’accensione

entro 1 ms. Un’ulteriore area della flash on-chip permette ai

progettisti di utilizzare la memoria per l’immagazzinamento

dei dati in modo non volatile, riducendo la necessità di me-

morie esterne.

Sebbene i primi FPGA erano praticamente composti da

blocchi logici “soft”, l’ampliamento del campo di applicazio-

ne di questi dispositivi ha spinto i produttori ad aggiunge-

re blocchi logici dedicati ad alte prestazioni per ottimizzare

l’uso dell’area del die. Uno degli elementi più comuni è l’in-

terfaccia SerDes (Serialiser/Deserialiser). Il blocco SerDes

(Fig. 4) è ora integrato in molte architetture FPGA.

Il consumo di energia degli I/O è diventato un elemento cri-

tico nella progettazione del sistema. Anche se l’invio di dati

in parallelo può assicurare un’elevata larghezza di banda,

l’uso di molteplici linee di dati che trasferiscono i bit in con-

temporanea può richiedere molta energia e dare origine a

problemi di l’integrità del segnale, in special modo quando

aumentano le velocità di clock. Gli I/O di tipo seriale posso-

no garantire una migliore integrità di segnale in presenza di

velocità di trasferimento dati superiori grazie all’adozione

dell’equalizzazione adattativa e di altre tecniche di condi-

zionamento del segnale. Adottando in genere livelli logici

con ridotta oscillazione della tensione, le interfacce seriali

possono contribuire a migliorare il rendimento energetico.

Ad esempio, il dispositivo ECP3 di Lattice consuma solo

110 mW a una velocità di trasferimento dati di 3,2 Gbps. Di

conseguenza, i canali seriali sono ora ampiamente usati per

le interfacce di memoria ad alta velocità, ol-

tre che per le comunicazioni da chip a chip e

da scheda a scheda.

Gli I/O seriali

Gli I/O seriali richiedono il supporto di bloc-

chi logici relativamente complessi che sa-

rebbero costosi da implementare sfruttando

esclusivamente la logica programmabile.

Blocchi logici SerDes I dedicati basati su

gate ASIC di tipo “hard” consentono una tra-

smissione del segnale più rapida e lo svilup-

po di circuiti operanti a velocità più elevate.

Questa logica è necessaria per convertire i

segnali che provengono da un bus paralle-

lo interno in una rappresentazione seriale

temporizzata e recuperano i dati da un col-

legamento seriale in ingresso. Integrando la

funzione SerDes in un hardware dedicato,

gli odierni FPGA mettono a disposizione una

quantità maggiore di logica programmabile da utilizzare per

l’applicazione finale.

I blocchi SerDes sono comuni a molte delle famiglie di FPGA

di fascia media e alta. Tra i prodotti che integrano blocchi

SerDes di possono annoverare i dispositivi Stratix di Altera,

ECP3 di Lattice e Virtex di Xilinx. Alcuni di questi FPGA sup-

portano velocità di trasferimento dati seriali fino a 28 Gbit/s

utilizzando una combinazione di tecniche di condiziona-

mento del segnale. Gli FPGA ottimizzati in termini di costi,

come quelli delle linee Cyclone di Altera, Mach XO2 di Latti-

ce, le famiglie di SoC Igloo di Microsemi e Spartan di Xilinx

spesso supportano interfacce di segnalazione a bassa ten-

sione come LVDS, ma nella maggior parte dei casi delega-

no l’implementazione delle funzionalità SerDes ai blocchi di

logica programmabile.

I dispositivi della serie Cyclone V di Altera forniscono il sup-

porto per la comunicazione seriale a velocità fino a 5 Gbps

per porta, per un massimo di 12 porte, in funzione del mo-

dello. Per facilitare l’implementazione delle funzioni SerDes,

i componenti integrano funzioni di codifica e decodifica

8B/10B a livello hardware per assicurare il supporto del più

diffuso formato di serializzazione dati e della protezione da-

gli errori nella logica ASIC cablata. Il supporto on-chip per

PCIe, Gen1 e Gen2, semplifica l’implementazione nel caso in

cui i sistemi devono interfacciarsi con PC e server.

Core di comunicazioni dedicati

Le comunicazioni dedicate e i core di utilità sono disponi-

bili negli FPGA ottimizzati in termini di costi per consentir-

ne l’utilizzo in applicazioni industriali e di consumo dove

sono previsti elevati volumi. La famiglia Mach XO2 di Lattice,

Fig. 3 – I dispositivi della serie MachX02 di Lattice prevedono una memoria flash on-chip