ANALOG/MIXED SIGNAL

PCB DESIGN

32

- ELETTRONICA OGGI 446 - GIUGNO 2015

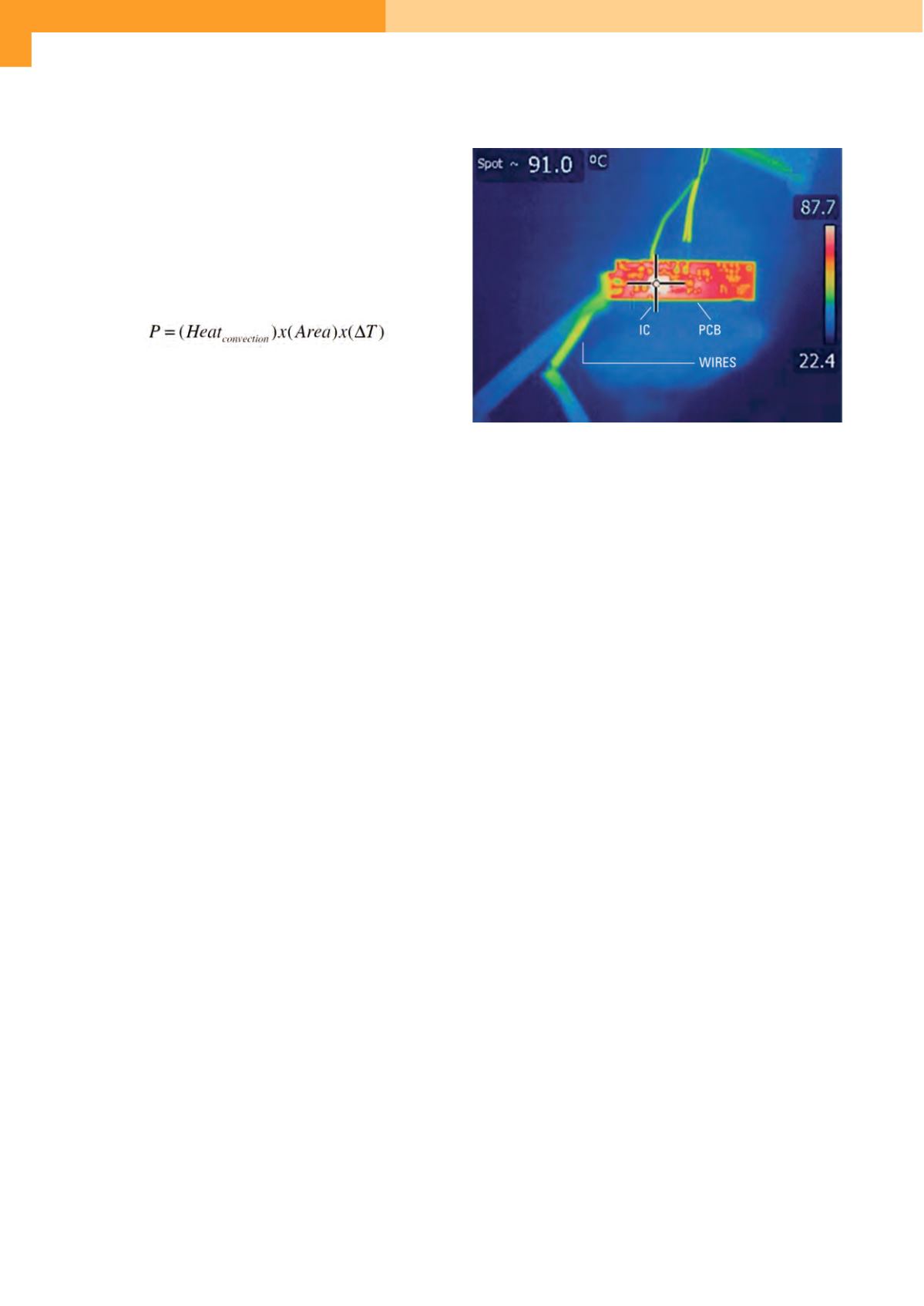

Questa immagine mostra l’efficacia nella distribuzione unifor-

me del calore dalla sorgente a tutte le superfici esposte della

scheda. In caso di dissipazione uniforme è possibile impiegare

questa formula per stimare la temperatura superficiale:

dove:

•

P è la potenza dissipata sulla scheda

•

Area è l’area della scheda (dimensioni x per y)

•

Δ

T è la differenza tra la temperatura superficiale e la tempe-

ratura ambiente

•

HeatCONVECTION è la costante di convezione

Revisione e rifinitura del progetto

Il posizionamento dei componenti dovrebbe essere eseguito

nell’ordine seguente: connettori, circuiti di potenza, circuiti

sensibili e di precisione, componenti critici e poi tutto il resto.

A questo punto lo schema elettrico ha tutti i suoi componen-

ti piazzati sulla scheda. La gerarchia di priorità nello sbroglio

è dettata dalle tensioni di alimentazione, dalla suscettibilità o

dalla generazione di rumore e dalla capacità di tracciamento

delle piste. In generale piste di larghezza 10-20 mils sono utiliz-

zate per trasportare correnti di 10-20 mA, mentre tracce da 5-8

mils per correnti inferiori a 10 mA. Le piste che portano segnali

ad alta frequenza (superiore a 3 MHz) e velocemente variabili

nel tempo devono essere disegnate con grande attenzione, in

particolare quando attraversano nodi ad alta impedenza.

A questo punto il layout dovrebbe essere controllato da un

responsabile del progetto per ritoccare le posizioni dei com-

ponenti e i percorsi delle piste in modo iterativo fino all’ottimiz-

zazione di tutti i vincoli di progetto. Il numero di strati dipende

dal numero di tensioni di alimentazione e dalla complessità del

circuito. Gli strati sono aggiunti a coppie a causa del metodo

di fabbricazione. Tra i fattori più importanti che influenzano

il funzionamento vi sono il layout dei segnali di potenza e dei

piani di alimentazione, lo schema di messa a massa e la pos-

sibilità di utilizzare la scheda come desiderato. Un’ispezione

finale dovrebbe verificare l’adeguata schermatura dalle sor-

genti di rumore dei nodi e dei componenti più sensibili, assi-

curarsi dell’esistenza della soldermask tra i pin e le vias e che

la serigrafia sia leggibile e concisa.

Quando si determina la distribuzione dei piani, è consigliabile

impiegare il primo strato interno sotto i componenti come pia-

no di massa e assegnare i piani di alimentazione agli altri livel-

li. Idealmente, la scheda dovrebbe essere simmetrica nell’allo-

cazione verticale dei piani rispetto al piano centrale. In questa

fase qualsiasi altro vincolo deve essere preso in considerazio-

ne al fine di correggere la scheda in base alle ultime revisioni.

Una lista delle modifiche dovrebbe essere creata e aggiornata

a ogni passo di revisione sino alla conclusione della scheda.

Durante tutte le fasi di esecuzione del layout dovrebbe essere

sempre utilizzato un sistema automatico di controllo dei vinco-

li di progettazione, o DRC (Design Rule Checker), per evitare

errori. Naturamente il DRC è in grado di segnalare solamente

gli errori per cui è stato programmato e l’insieme di regole di

verifica cambia spesso tra i vari progetti.

L’insieme di regole basilari dovrebbe comprendere: la spazia-

tura tra componente e componente, la presenza di maglie non

connesse (ogni nodo del circuito è identificato da un nome

univoco nella netlist), cortocircuiti, violazioni della spaziatura

minima, vias troppo vicine ai pad di saldatura o troppo vicine

tra loro e violazioni della clearance.

Moltre regole aggiuntive possono essere impostante nel DRC

per assicurarsi un progetto robusto. Altre regole generali in-

cludono: mantenere gli spazi liberi sopra i 5 mils, evitare di

piazzare le vias all’interno dell’area coperta dai pad di compo-

nenti a montaggio superficiale e assicurarsi che la soldermask

sia presente su tutte le piazzole da saldare.

Infine, può essere utile per i progettisti comprendere i fattori

che incrementano il costo di un circuito stampato. Una scheda

normale è a 2 o a 4 strati, priva di fori di diametro inferiore a

10 mils, con spaziatura e larghezza delle piste di almeno 5 mils,

realizzata in FR-4 di spessore 0,062 pollici e con uno spessore

del rame di 35 micron (1 oz).

I fattori che incrementano il costo sono: l’aggiunta di altri strati,

uno spessore maggiore o minore della scheda o delle piste di

rame, vias nel pad, vias piene, vias cieche o sepolte e un tem-

po di fabbricazione minore.

n

Note

[1] Queste caratteristiche speciali includono: intagli, sago-

mature, smussature, vias riempite sotto i pad (impiegate ad

esempio nei package di tipo BGA che hanno file di pad sotto

il componente) vias cieche o sepolte, rifinitura o livellamento

della superficie, tolleranze sui fori, numero di strati e così via.

Fig. 4 – Immagine termica di un circuito integrato di regolazione dell’a-

limentazione su un circuito stampato