POWER

TELECOMM/DATACOMM SUPPLY

40

- ELETTRONICA OGGI 457 - OTTOBRE 2016

sino a 12 fasi e sfasare le uscite di

30 gradi mediante un chip esterno

con clock come LTC6902.Inoltre,

l’apposito loop ausiliario interno

di LTC7851/-1 equalizza la corren-

te tra le fasi quando queste sono

collegate in parallelo, consentendo

una condivisione precisa della cor-

rente fra più circuiti integrati, sia

nello stato stazionario sia durante

un evento transitorio; in tal modo

non solo si evita che in un canale vi

sia una percentuale eccessiva della

corrente di carico ma si semplifica

il progetto termico. Il dispositivo

funziona con tensione di alimenta-

zione VCC compresa fra 3V e 5,5V ed è stato progettato

per eseguire la conversione in discesa a partire da una

tensione d’ingresso compresa fra 3V e 27V. Genera da

una a quattro tensioni di uscita indipendenti comprese

fra 0,6V e 5V. La sua architettura di controllo della moda-

lità di tensione ne consente il funzionamento a frequenza

costante, selezionabile fra 250kHz e 2,25MHz; in alterna-

tiva, lo si può sincronizzare con un clock esterno nella

stessa gamma di frequenze. La corrente di uscita viene

rilevata monitorando la caduta di tensione ai capi dell’in-

duttore di uscita (DCR) ai fini della massima efficienza op-

pure utilizzando un apposito resistore di basso valore. Gli

amplificatori differenziali incorporati assicurano una ef-

fettiva rilevazione in remoto della tensione di tutte le usci-

te per ottenere una regolazione di elevata precisione. Il

circuito integrato LTC7851-1 è simile al modello LTC7851,

ma con un guadagno inferiore dell’amplificatore di rile-

vazione della corrente, ideale quindi per applicazioni di

treni di dispositivi di potenza utilizzando un DrMOS con

rilevazione interna della corrente. Tra le ulteriori funzioni

per ciascuna fase si possono segnalare le seguenti: moni-

toraggio della corrente, regolazione del limite di corrente,

avvio graduale o rilevamento dell’uscita programmabile

e segnali di “power good” individuali. Il dispositivo mantie-

ne una precisione della tensione di uscita pari a ±0,75%

in un intervallo di temperature di

funzionamento da –20 °C a +85 °C

ed è disponibile in un contenitore

QFN da 5mm x 9mm a 58 pin. Va

tenuto presente che un riferimento

preciso ben progettato può ridurre

notevolmente la capacità del con-

densatore bulk di uscita necessa-

rio per soddisfare i requisiti relati-

vi alla risposta al transitorio degli

odierni ASIC e altri dispositivi a se-

miconduttore personalizzati. La fi-

gura 1 riporta uno schema sempli-

ficato del dispositivo, che converte

un ingresso compreso tra 10V e

14V in un’uscita a 0,95V e 160A

utilizzando DrMOS per il treno di dispositivi di potenza.

Efficienza

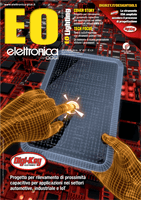

La curva dell’efficienza di LTC7851 rappresentata in fi-

gura 2 corrisponde allo schema circuitale della figura

1 in cui una tensione d’ingresso di 12V viene conver-

tita a 0,95V con corrente di uscita sino a 160 ampere.

Sono possibili valori dell’efficienza sino al 94%.

Bilanciamento di corrente

Quando si collegano in parallelo più canali di

LTC7851/-1 per pilotare un carico comune, è essen-

ziale una condivisione precisa della corrente di uscita

per ottenere efficienza e prestazioni ottimali; in caso

contrario, se uno stadio eroga più corrente di un altro,

vi sarà una differenza di temperatura tra i due stadi

e ciò potrebbe comportare un valore maggiore della

Rds(On) dell’interruttore, efficienza inferiore e un mag-

giore valore efficace del ripple. Un disadattamento

anche di piccola entità in uno schema multifase può

ridurre notevolmente la potenza totale disponibile.

Per applicazioni multifase a uscita singola, LTC7851/-

1 incorpora un loop ausiliario di condivisione della

corrente, in cui la corrente dell’induttore viene cam-

pionata a ogni ciclo. Al pin I

AVG

viene eseguita la me-

dia dell’uscita dell’amplificatore di rilevazione della

corrente del controller principale. Un condensatore di

piccola capacità (in genere 100pF) , collegato da I

AVG

a

GND, mantiene una tensione corrispondente alla cor-

rente media istantanea del controller principale.

I pin I

AVG

delle fasi master e slave sono collegati fra

di loro e ciascuna fase slave integra la differenza tra

la sua corrente e quella del master. Per ciascuna fase,

l’uscita dell’integratore viene sommata in modo pro-

porzionale alla tensione dell’amplificatore di errore

del sistema (COMP), regolando il duty cycle di tale

fase per equalizzare le correnti. Quando più circuiti in-

tegrati sono collegati in serie, i pin I

AVG

sono collegati

fra di loro, causando uno sbilanciamento della corren-

Fig. 3 – Bilanciamento di corrente delle quattro fasi

per una singola uscita di 0,95V a 160A

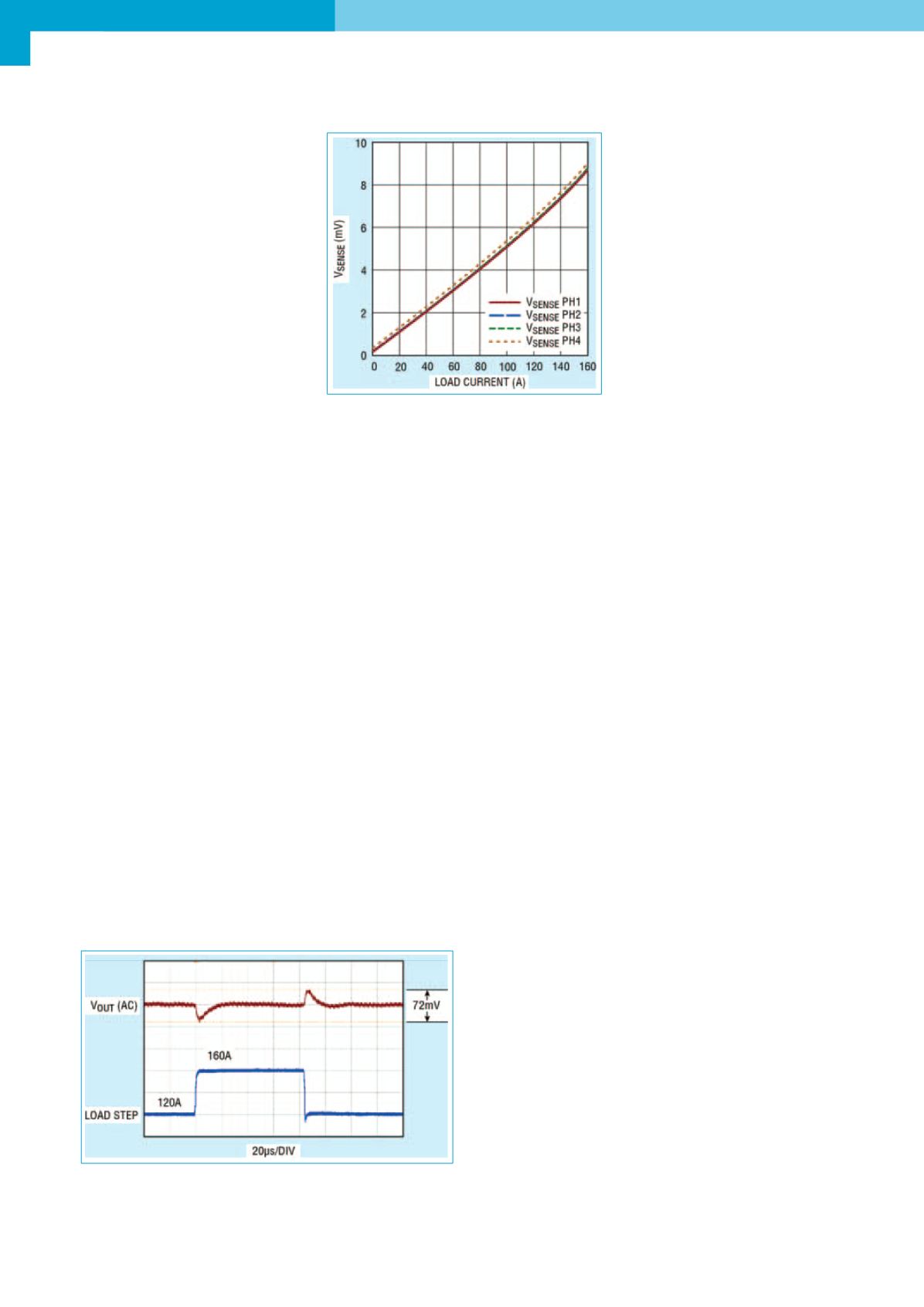

Fig. 4 – Risposta al transitorio con un carico a gradino da 40A per il

circuito della figura 1