DIGITAL

mimo

57

- ELETTRONICA OGGI 444 - APRILE 2015

Communications per quanto riguarda il suo nucleo centrale:

grazie alla piattaforma Argos della Rice University è stato

possibile utilizzare un massimo di 24 FPGA connessi a 96

antenne usando la. Un framework Python personalizzato

sviluppato da Mango Communications controlla e raccoglie

i dati da ogni nodo nella matrice in tempo reale. La combi-

nazione di tool sviluppati da Mango e dalla Rice Universi-

ty permette di analizzare in maniera approfondita lo stack

wireless, inclusi di dati originali del canale necessari per

caratterizzare il MIMO massivo.

Una caratteristica chiave dell’implementazione 802.11 de-

dicata è la capacità di trasmettere in tempo reale parametri

di basso livello in banda base, come i guadagni AGC, le sti-

me sui canali e i contenuti dei pacchetti originali (anche dei

pacchetti con errori) da tutte le antenne in ricezione. Questa

caratteristica del progetto di riferimento consente alla ma-

trice Argos di Rice di comportarsi come un punto di acces-

so (AP) standard conforme allo standard 802.11, fornendo

la connettività Internet ai dispositivi WiFi commerciali (ad

esempio, smartphone, tablet o laptop) e raccogliendo simul-

taneamente i dati dei canali fra le antenne della matrice e

ciascun client, il tutto in tempo reale. Gli FPGA di Xilinx sono

cruciali per garantire il funzionamento in tempo reale in cor-

rispondenza di ciascuna antenna. Essi condensano i dati

raccolti da ciascuna antenna all’interno delle caratteristiche

dei canali clienti che un’applicazione dedicata può trasmet-

tere in tempo reale ed analizzare.

Componenti a livello di sistema

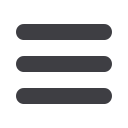

WARP – Wireless Open-Access Research Platform, è una

piattaforma wireless programmabile, scalabile ed espandi-

bile adatta alla prototipazione di reti wireless avanzate. Essa

abbina hardware programmabile ad alte prestazioni con un

database open source di progetti di riferimento e di materia-

li di supporto. Un componente centrale all’interno del siste-

ma di misura dei canali MIMO massivi è la piattaforma har-

dware WARP v3 di Mango Communications. La piattaforma,

ideata per la prototipazione in tempo reale di nuovi progetti

wireless, integra un FPGA Virtex 6 di Xilinx ad alte prestazio-

ni, due interfacce RF flessibili e diverse periferiche, incluse

DRAM DDR3 e due interfacce Gigabit Ethernet da 1 Gbps.

La scheda WARP v3 può essere estesa a quattro interfacce

RF completamente programmabili con connessioni digitali

indipendenti in banda base verso l’FPGA (Fig. 1).

Per studiare i sistemi MIMO massivi, è necessario alloca-

re simultaneamente più nodi WARP v3 con alimentazione,

temporizzazione e connettività Ethernet condivise. Questo

requisito è stato soddisfatto dal progetto Argos dell’Univer-

sità di Rice. La matrice v2 Argos è una combinnazione di

24 nodi WARP-v3 con quattro antenne (Fig. 2). Essa è stata

progettata per supportare un’ampia varietà di esperimen-

ti MIMO massivi, ed è particolarmente adatta per acquisire

più misure simultanee sui canali, lungo tutte e 96 le antenne

della matrice. L’FPGA in corrispondenza di ciascun nodo

WARP v3 fornisce la potenza di elaborazione necessaria in

prossimità delle interfacce RF. In una configurazione MIMO

massiva come quella del progetto Argos, è necessario ela-

borare un’enorme quantità di dati. Ad esempio, quando ri-

ceve 40 MHz di banda, ciascuna interfaccia RF su WARP

Fig. 1 – L’hardware WARP v3 con il modulo FMC con due radio mette

a disposizione un FPGA di grandi dimensioni, Quattro interfacce RF,

memoria e due connessioni Ethernet