29

- ELETTRONICA OGGI 438 - LUGLIO/AGOSTO 2014

TECH INSIGHT

SoI

zione delle geometrie

senza intervenire paral-

lelamente anche su altri

parametri porta a non

pochi inconvenienti. Il

primo di questi è dato

dal progressivo aumen-

to delle correnti paras-

site, che comporta un

costante aumento della

potenza dissipata pro-

prio a causa delle cor-

renti di fuga.

Come si può vedere

dall’istogramma di figu-

ra 5, infatti, già una volta

raggiunto il nodo dei 28

nm la potenza dissipata

a causa delle correnti

parassite supera quel-

la dovuta alle normali

commutazioni dei chip,

ed è oggi il vero cruccio

che condiziona gli ulte-

riori sviluppi tecnologi-

ci. Ecco il motivo per

cui si vanno cercando

soluzioni alternative, in

grado di abbattere pro-

prio le correnti paras-

site.

Una soluzione che si

sta recentemente impo-

nendo in tale direzione

è l’impiego della tecni-

ca silicon-on-insulator

abbinata al ricorso a

transistor Mosfet del

tipo “fully depleted” o

FD, dando luogo alla

denominazione

di

FD-SOI per questa tec-

nologia. Fra le varie

aziende che stanno

utilizzando tale tecno-

logia va citata senz’al-

tro STMicroelectronics,

che con i propri part-

ner ha introdotto già dal

2012 nei propri labora-

tori le prime realizzazio-

ni di chip di tipo FD-SOI.

Tale tecnica permette

infatti di partire da un

processo di tipo pla-

nare che consente di

ottenere tutti i vantaggi

delle geometrie ridotte

semplificando nel con-

tempo il processo pro-

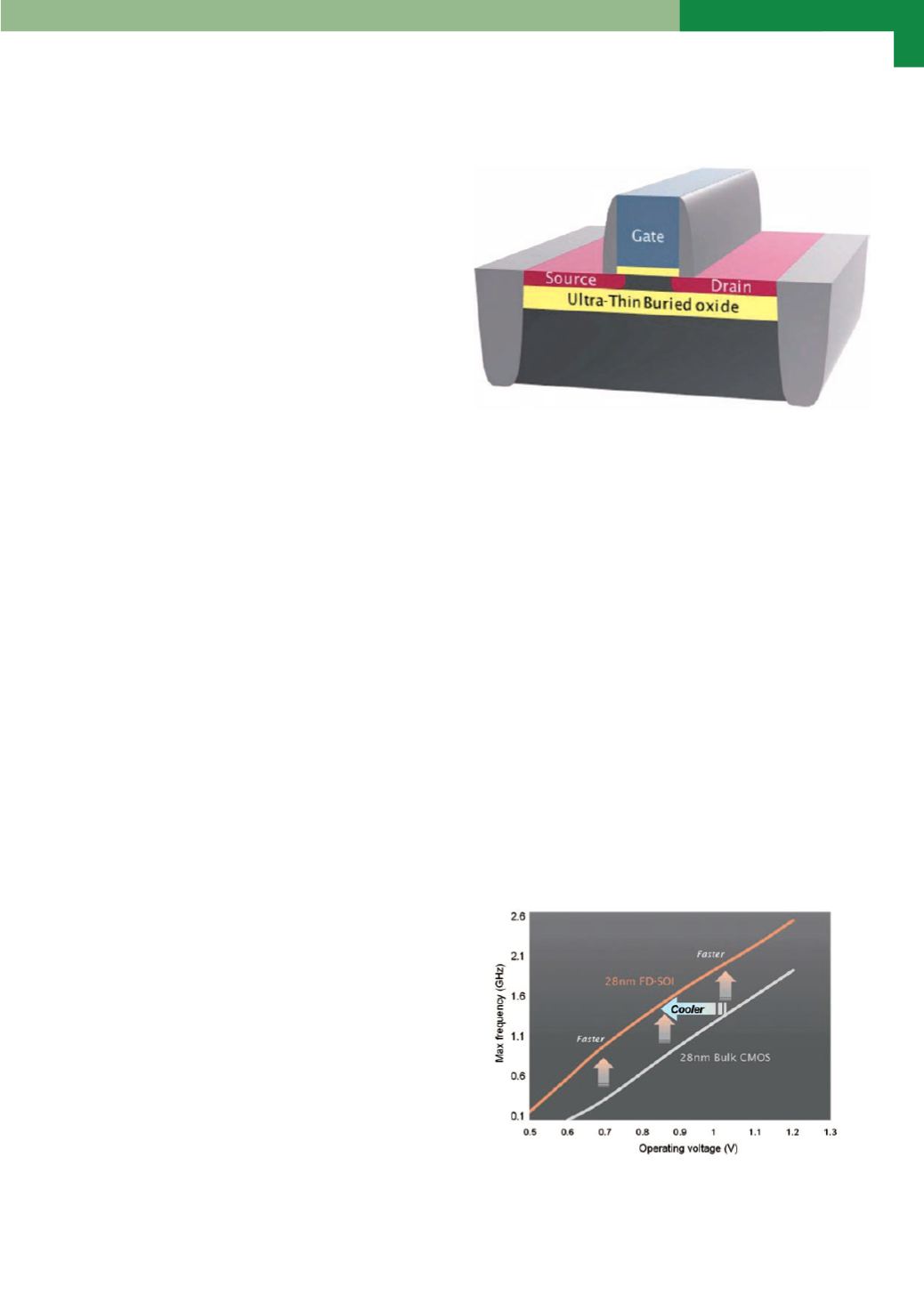

duttivo. La struttura di

base è quella visibile

in figura 6: il transistor

Mosfet viene realizzato

entro un sottile strato,

completamente separa-

to dal substrato grazie

non solo alla presenza

degli isolamenti laterali,

ma soprattutto alla pre-

senza di uno strato iso-

lante di “ossido sepolto”

o Buried Oxide (BOX).

La denominazione FD

di “Fully Depleted” deri-

va dal fatto che, con-

trariamente ai normali

transistor, il sottilissimo

strato di semicondutto-

re che si trova al di

sotto del dielettrico di

gate (del tipo ad alta

costante dielettrica)

non contiene droganti.

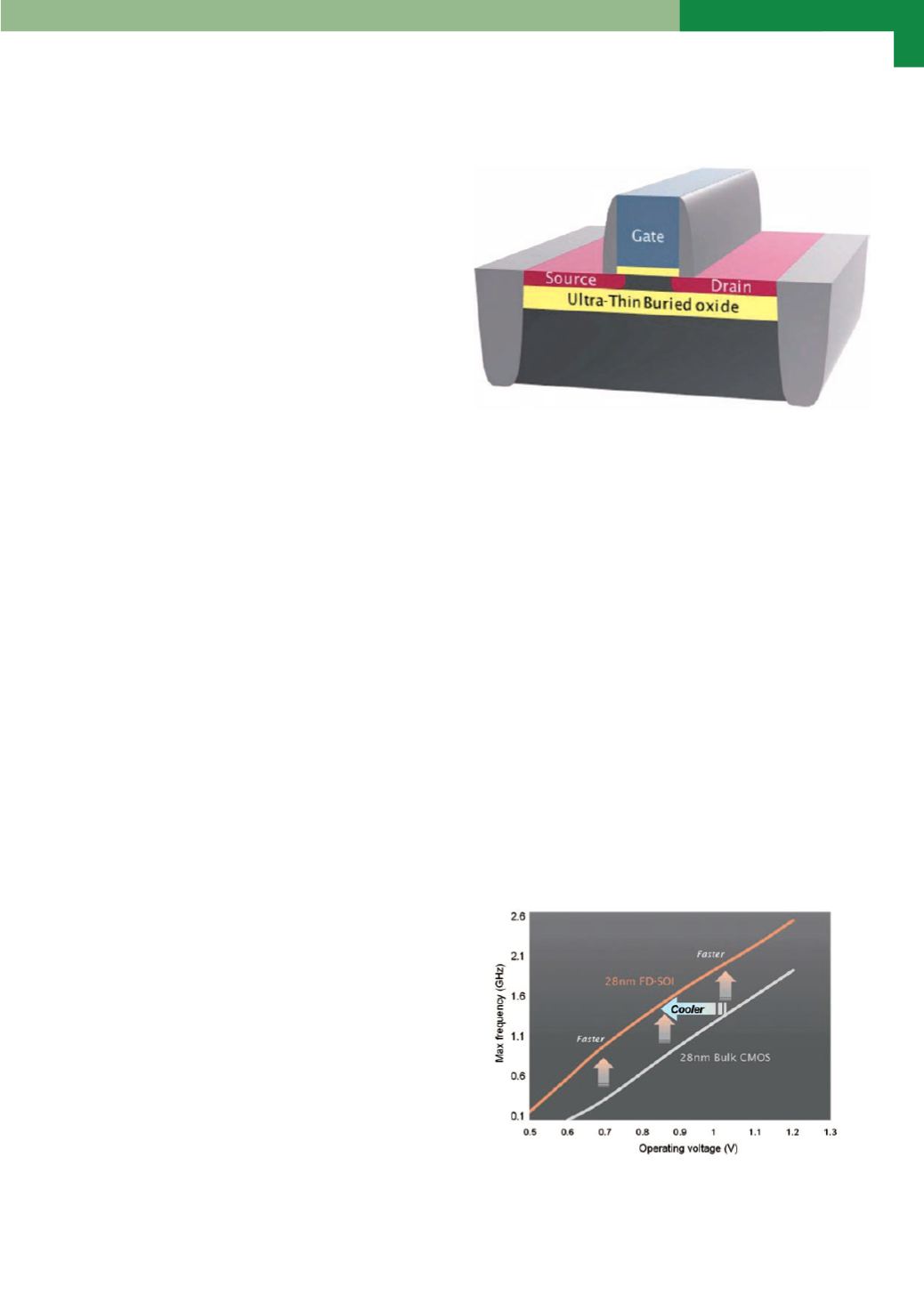

Si è visto che una strut-

tura di questo tipo è

in grado di operare a

frequenze del 30% più

elevate di quelle otteni-

bili con transistor dalle

medesime dimensioni

ma realizzati in tecno-

logia “bulk” tradizio-

nale con isolamento a

giunzione (Fig. 7) con il

vantaggio di non dover

ricorrere alla comples-

sità delle strutture del

tipo FinFet. Non solo,

ma – come si può vede-

re dalla medesima figu-

ra, è possibile operare

a minor tensione senza

penalizzazione di velo-

cità, a tutto vantaggio

del contenimento della

potenza dissipata.

Inoltre, è possibile

migliorare ulteriormen-

te il controllo on-off

del transistor agendo

sulla polarizzazione del

substrato, al di sotto

dell’ossido BOX, che

può fungere da “buried

gate”. Questa struttura,

proprio poiché viene

realizzata entro uno

strato di silicio estre-

mamente sottile, viene

anche spesso chiamata

ET-SOI, da Extremely-

Thin SOI. Grazie a que-

sto piccolo spessore

(si parla anche di “tran-

sistor superficiale”) il

gate riesce con estre-

ma facilità a rimuovere

ogni carica dal canale

conduttivo, miglioran-

do non solo lo stato

di off, ma accelerando

notevolmente la fase di

svuotamento del cana-

le. Si è altresì visto che,

adottando un’oppor-

tuna combinazione di

valori delle due tensioni

di gate superiore e infe-

riore, si possono otte-

Fig. 6 – Struttura di base del processo FD-SOI messo a punto da

STMicroelectronics

Fig. 7 – Significativo è il vantaggio ottenibile con la nuova tecnologia

FD-SOI rispetto alla bulk-Cmos a pari dimensioni