28

- ELETTRONICA OGGI 438 - LUGLIO/AGOSTO 2014

TECH INSIGHT

SoI

della tensione applica-

ta, ma anche di ridur-

re le capacità parassite

e quindi di aumentare

la frequenza operati-

va dei circuiti, e con-

seguentemente ridurre

la potenza dissipata a

pari frequenza, ottenen-

do inoltre significative

riduzioni nell’area del

chip.

Proprio poiché le tecni-

che classiche di realiz-

zazione di circuiti isola-

ti ponevano non poche

difficoltà realizzative,

l’industria dei semicon-

duttori ha da alcuni anni

messo a punto nuove

tecniche per realizzare

circuiti di tipo SOI, e le

realizzazioni commer-

ciali si sono susseguite

a partire soprattutto da

una decina di anni fa,

legate essenzialmente a

molti prodotti di punta.

Ne sono un esempio le

realizzazioni in tecnolo-

gia SOI di processori e

GPU da parte di AMD e

IBM (Fig. 2).

Le difficoltà realizzative

comunque permango-

no, e portano a ulteriori

costi di fabbricazione,

che fra l’altro hanno

indotto taluni costrutto-

ri (Intel ne è un esem-

pio) a sperimentare

inizialmente il ricorso

alla tecnologia SOI per

la soglia dei 22 nm per

poi preferire strutture

FinFet-3D tri-gate tran-

sistor per ridurre i costi

produttivi a pari presta-

zioni.

Non solo, ma grazie al

fatto di poter realizzare

i componenti entro un

sottile strato di silicio, vi

è la possibilità di miglio-

rare ulteriormente e in

maniera significativa le

caratteristiche dell’in-

tero circuito sfruttando

la possibilità di isolare

completamente l’uno

dall’altro i singoli tran-

sistor integrati inseren-

do dei “canali” di ossido

isolante che fungono

così da “pareti isolanti”

fra i vari componenti,

con abbattimento delle

correnti parassite inter-

componente, abolizione

del latchup e minimiz-

zazione delle capacità

parassite, a tutto van-

taggio della frequenza

operativa e con la pos-

sibilità di ridurre ulte-

riormente la tensione

di lavoro del circuito

e contenere la potenza

dissipata.

Un chiaro esempio è

rappresentato

dalla

sezione di una tipica

struttura utilizzata da

Toshiba nei driver da

600V e in altre realiz-

zazioni che integrano

dispositivi di potenza

quali gli Igbt, nei quali

l’obiettivo di isolare gli

elementi di pilotaggio

Cmos a bassa tensione

dai finali a varie cen-

tinaia di volt ha porta-

to alla scelta di ricor-

rere ad una tecnologia

s i l i con-on- i nsu l a t or

che utilizzava l’ossido

di silicio anche per l’i-

solamento laterale dei

componenti. La strut-

tura risultante è quella

visibile in figura 3.

Con la tecnica dell’iso-

lamento a giunzione di

tipo classico si sareb-

bero dovute utilizzare

aree decisamente più

ampie per ospitare le

regioni di deplezione

delle giunzioni in pola-

rizzazione inversa, men-

tre grazie all’isolamento

a ossido è stato utilizza-

to solo lo 0.7% dell’area

altrimenti necessaria

per l’isolamento a giun-

zione. Grazie al ricor-

so alla tecnologia SOI

si sono ottenute den-

sità di corrente pari a

ben 100A/cm

2

. È il caso

ad esempio della serie

di inverter trifase da

2A/240 Vac in tecno-

logia SOI che possono

essere pilotati diretta-

mente da microcontrol-

ler, mostrati in figura 4.

La tecnica FD-SOI

Il motivo per cui varie

aziende stanno di fatto

“riscoprendo” i vantag-

gi derivabili dal ricor-

so alla tecnologia SOI

(anche se da un nuovo

punto di vista) dipende

soprattutto dal fatto che,

perseguendo la sola via

della progressiva ridu-

Fig. 4 –Gli inverter da 2A/240 Vac di Toshiba in tecnologia SOI, pilotabili

direttamente da microcontroller

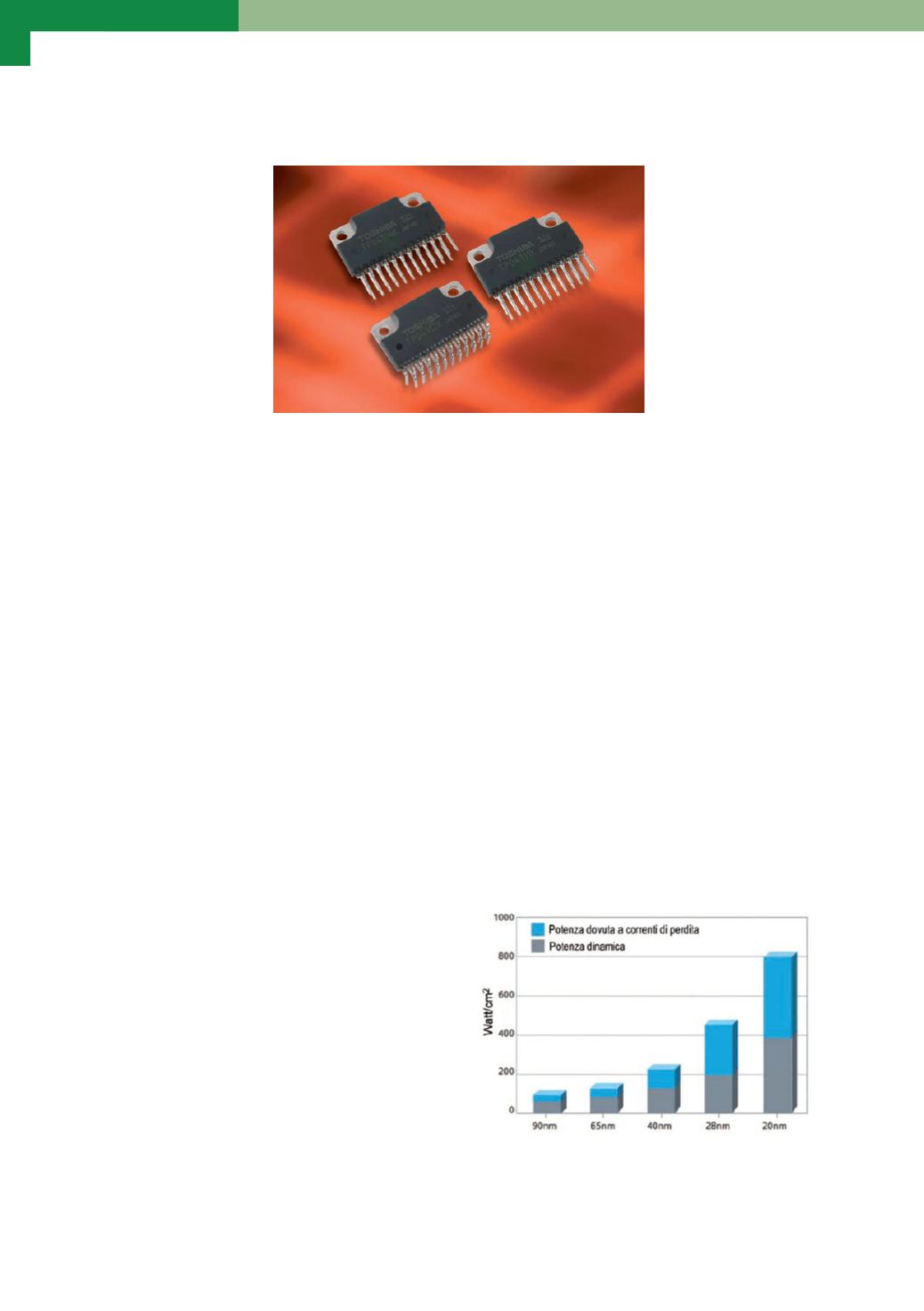

Fig. 5 – Con la progressiva riduzione delle geometrie, la frazione di

potenza dissipata a causa delle correnti parassite supera quella dovuta

alla normale commutazione (Fonte: International Business Strategies)