POWER 7 - marzo 2015

XI

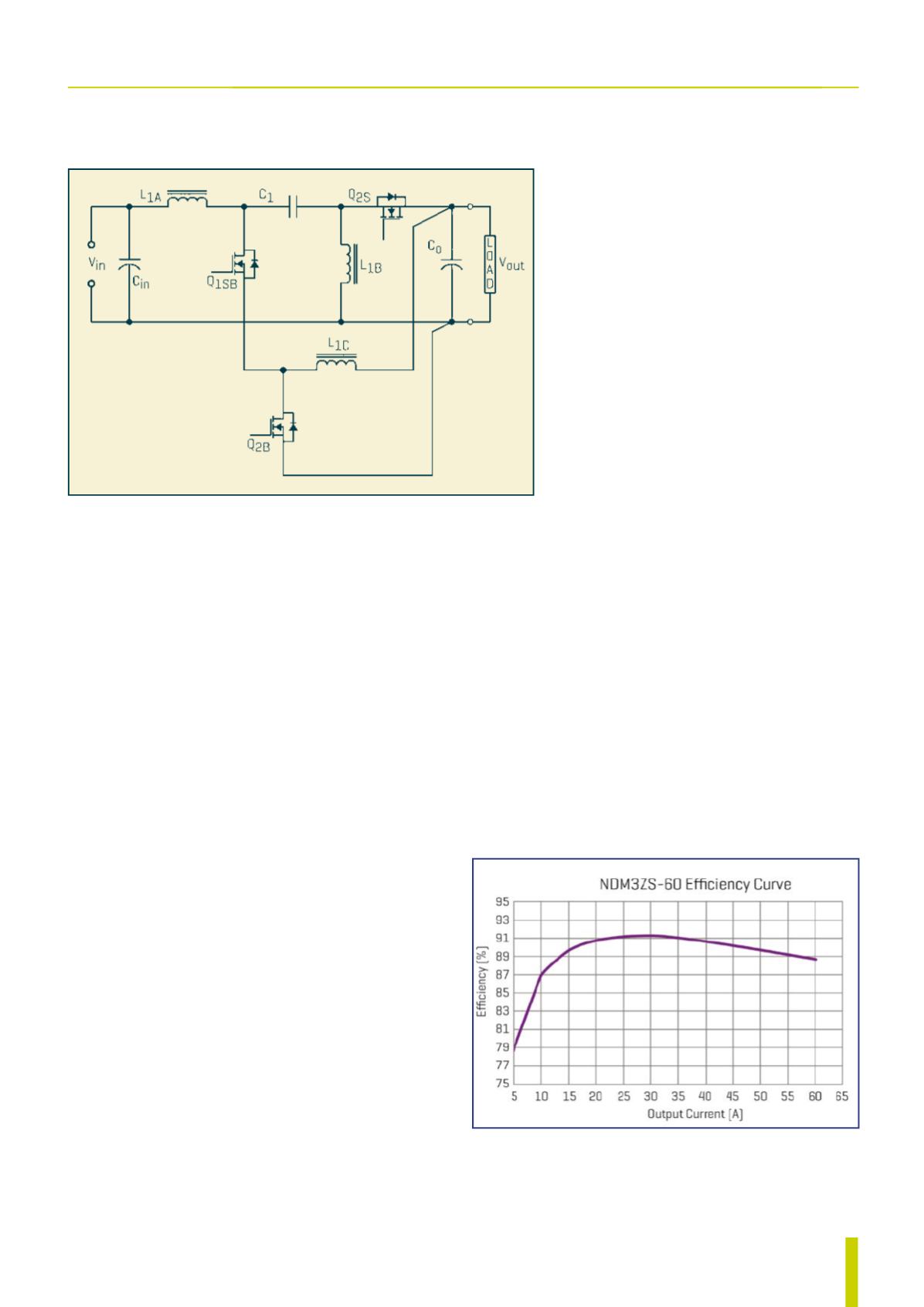

SEPIC-FED BUCK

Limiti delle topologie POL esistenti

La topologia più comune utilizzata nelle applicazioni PoL è

il convertitore buck sincrono. In questo caso l’utilizzo di un

MOSFET low-side al posto di un diodo contribuisce a ridur-

re in modo significativo le perdite, con conseguente miglio-

ramento dell’efficienza di conversione rispetto a un conver-

titore buck tradizionale. Lo schema di un convertitore buck

sincrono è riportato in figura 1.

Questa topologia richiede un circuito di pilotaggio del MO-

SFET più complesso per controllare entrambi i commutato-

ri. Inoltre, è necessario assicurarsi che entrambi i MOSFET

non siano accesi (turn-on) contemporaneamente, in quanto

si potrebbe creare un corto circuito diretto dalla tensione di

ingresso (Vin) a massa con conseguenze potenzialmente ca-

tastrofiche. Questo tipo di corto circuito è anche noto come

conduzione incrociata (cross-conduction) o shoot-through.

L’impiego di un MOSFET al posto di un diodo di ricircolo

(catch o free-wheeling diode), oltre a ridurre le perdite per

conduzione, consente un flusso bidirezionale della corren-

te dell’induttore. In presenza di carichi di valore ridotto, il

convertitore buck sincrono continua dunque a funzionare

in modalità CCM (Continuous Conduction Mode), mentre

un convertitore buck tradizionale entra in modalità DCM

(Discontinuous Conduction Mode). Un convertitore buck

sincrono può dunque garantire un’elevata efficienza per

correnti di uscita a valore elevato, ma è tutt’altro che effi-

ciente per bassi valori di potenza di uscita.

Ciò significa che il miglioramento dell’efficienza per carichi

di valore ridotto e per correnti di uscita elevate, una priorità

per le apparecchiature di rete della prossima generazione,

rimane un problema irrisolto.

La necessità di fornire una corrente dinamica di notevole

intensità, con una tensione regolata in maniera

molto precisa, permette di evidenziare un’altra

limitazione delle topologie esistenti. Nel caso si

utilizzi un convertitore buck, transistori di carico

di notevole entità danno origine a significative va-

riazioni della tensione di uscita.

Poiché la velocità di variazione della corrente

dell’induttore non è pari a quella della corrente

di carico, il condensatore di uscita deve fornire

la corrente necessaria per alimentare il carico

durante i transistori di quest’ultimo. La tensione

di uscita, quindi, varierà rispetto al valore nomi-

nale stabilito, a causa della scarica del condensa-

tore. Viceversa, un transitorio di carico veloce di

tipo “step-down” produrrà una sovraelongazione

(overshoot) di tensione, imputabile alla carica

del condensatore.

A causa del funzionamento sincrono a frequen-

za costante, il controllore non può reagire immediatamente

per accendere il commutatore di controllo a seguito di una

variazione a gradino della corrente di carico. Il controllore

deve quindi attendere il successivo impulso di clock prima

che il commutatore di controllo sia nuovamente acceso.

L’ampiezza di banda finita del compensatore lineare – pro-

gettata in modo da essere una frazione della frequenza di

commutazione allo scopo di garantire la stabilità del sistema

– impedisce alla tensione di controllo di aumentare con una

velocità sufficiente. A causa di questi due fattori combinati,

l’integrale della scarica del condensatore è maggiore rispet-

to al caso ideale.

Poiché l’ampiezza di banda del compensatore è progettata

in funzione della frequenza di commutazione, una soluzione

ovvia per affrontare le problematiche appena sopra deline-

ate è incrementare la frequenza di commutazione del con-

Fig. 2 – Schema di un convertitore SEPIC-fed buck

Fig. 3 – Andamento dell’efficienza in funzione della

corrente di uscita di un convertitore SEPIC-fed buck

da 60A con ingresso a 12V e uscita a 1V