EON

EWS

n

.

618

-

APRILE

2018

20

circa 15 anni fa da Infineon,

ma attualmente sta avendo

un vero e proprio revival

come modo efficace per so-

vrapporre i wafer uno sopra

l’altro. Il processore Apple

A10, per esempio, utiliz-

za la tecnologia fan-out di

TSMC, chiamata inFO, per

sovrapporre la memoria

DRAM alla CPU.

La tecnologia

più adatta per ogni

building block

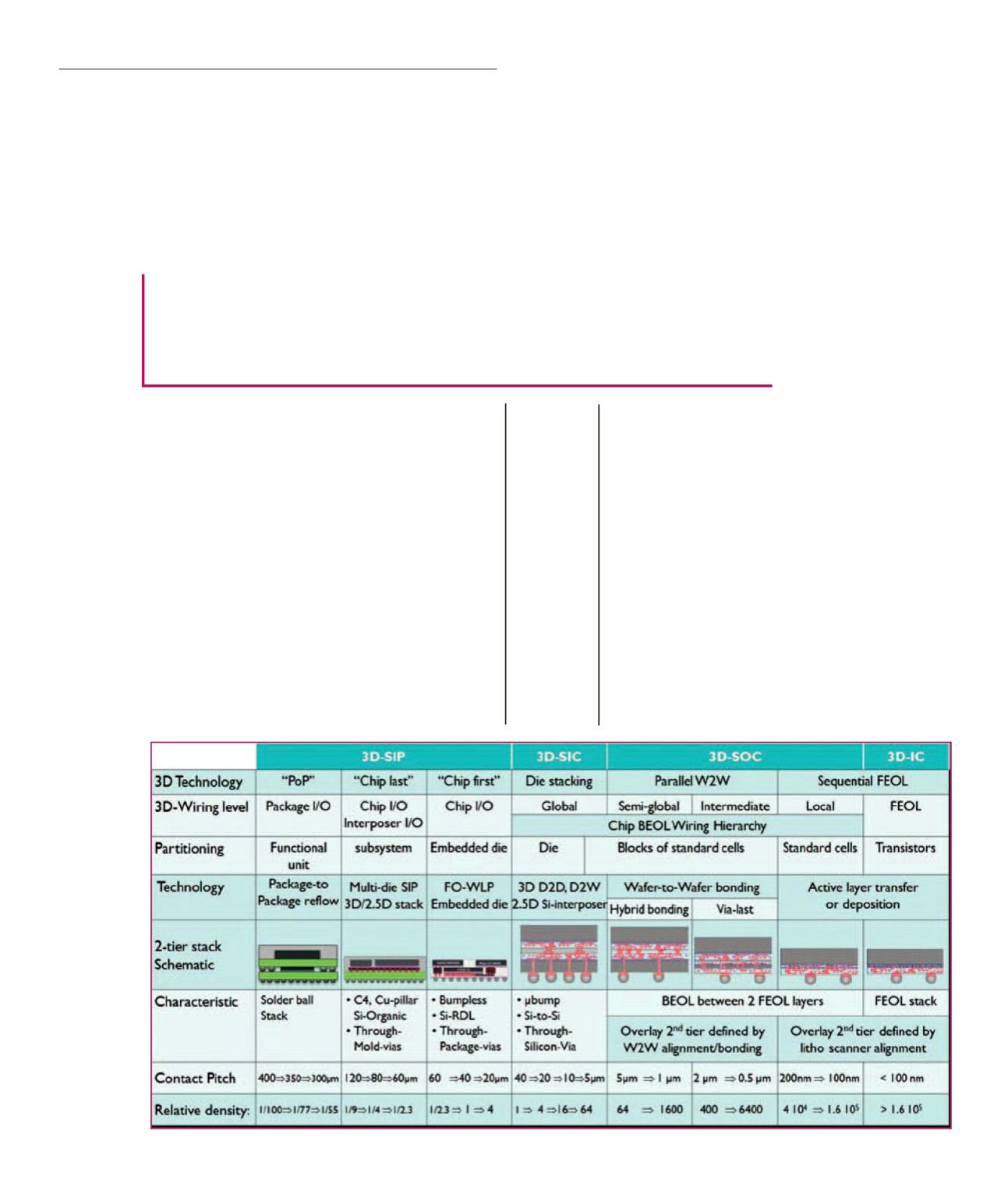

Nei prossimi anni vedre-

mo l’uso della tecnologia

3D per i chip in una gam-

ma sempre più ampia di

applicazioni, specialmente

laddove tali applicazioni

richiedono una elevata di

potenza di calcolo e ca-

pacità di memoria. Questi

impieghi comprenderanno

server multi-core e applica-

zioni relative all’intelligenza

artificiale. I sistemi diven-

teranno anche sempre più

“eterogenei”, il che significa

che la tecnologia 3D è es-

senziale. Un sistema ete-

rogeneo è costituito da vari

componenti specializzati,

come memorie, sensori di

immagine, elettronica III-V

Il 3D sul mercato

Nel 2017 abbiamo visto

iniziare a comparire la tec-

nologia 3D per i chip in una

gamma di diversi prodotti

commerciali. Per esempio,

l’iPhone 8 utilizza il senso-

re di immagine “stacked” di

Sony. Questo sensore offre

una qualità unica delle im-

magini sia per le foto che

per i video perché il sen-

sore di immagine, il chip di

elaborazione e la memoria

sono stati raggruppati per

creare una singola unità.

Il 3D è anche la strada da

percorrere per la memoria.

Si consideri, per esempio,

l’uso crescente di moduli a

elevata larghezza di banda.

Questi moduli contengo-

no 4 o 8 chip di memoria

DRAM sovrapposti sul chip

del processore. Nel 2017

sia AMD che Nvidia hanno

portato sul mercato potenti

processori basati su questo

principio. Questi processori

possono essere utilizza-

ti in laptop di fascia alta,

così come per applicazioni

connesse all’intelligenza

artificiale. Il 2017 ha inoltre

fornito un notevole impulso

alla tecnologia “fan-out wa-

fer-level packaging” (WLP).

Il fan-out WLP dovrebbe

essere considerato come

il passaggio logico suc-

cessivo al WLP standard,

affrontando il problema del

crescente disallineamento

e del gap di interconnessio-

ne tra chip e circuito stam-

pato. I chip sono tagliati da

un wafer di silicio e trasferiti

su un wafer di supporto,

dove sono posizionati più

distanti rispetto al wafer

originale. Il wafer ricostrui-

to viene quindi rivestito con

un composto epossidico,

uno strato di ridistribuzione

e sfere di saldatura. La tec-

nologia è stata sviluppata

Nuove opportunità

con la tecnologia 3D

Il 2017 ha visto una svolta decisiva per la tecnologia 3D per i chip

nei prodotti commerciali. Prima di allora l’industria era sembrata piuttosto

scettica rispetto a questa tecnologia, ma ora sta cominciando a rendersi

conto che il 3D non deve necessariamente costare di più. Crea, invece,

nuove possibilità e opportunità

Lo scenario

per la tecnologia

3D per i chip

prospettato

da imec

E

RIC

B

EYNE

Fellow e program director 3D system

integration - imec

T

ECNOLOGIE