DIGITAL

MCU

42

- ELETTRONICA OGGI 460 - MARZO 2017

e i Multiple-output Capture Compare (MCCP) possono co-

mandare i motori BLDC sollevandone la CPU e ottenere così

maggior efficienza di elaborazione riducendo i consumi. A

tal scopo, è stato aggiornato il tool Microchip MPLAB Code

Configurator, in modo da poter ripartire al meglio

le risorse fra la CPU e i core periferici. Ci sono

diversi package a partire da Qfn e Ssop a 20 pin

e 4x4 mm fino a 28, 36 e 40 pin da 5x5 e 6x6 mm,

dove la memoria Flash a bordo aumenta da 16

kByte a 32 o 64 kByte. A bordo c’è un ADC SAR

con risoluzione di 12 bit e velocità di 200 kSps e

un DAC con risoluzione di 5 bit. Alimentabile da

2,0 a 3,6 V, consuma 5 µA in Standby e 500 nA in

modalità Sleep.

Crittografia hardware

La stessa Microchip ha rilasciato in primavera il microcon-

trollore a 32 bit CEC1302 Cryptography-Enables, che incor-

pora un motore di crittografia hardware pensato per offrire

la massima sicurezza nelle applicazioni IoT che necessitano

dell’autenticazione durante le transazioni. Oltre a proteggere

i dati utente sensibili, la crittografia serve anche a difendere

il firmware dei sistemi dai software maligni (malware) e dagli

attacchi degli hacker e l’implementazione a livello hardware

offre maggior velocità e minori consumi rispetto alle analo-

ghe soluzioni puramente software. Il core è ARM Cortex-M4

a 32 bit, con clock di 48 MHz, e si affianca a 128 kByte di

memoria Sram, 32 kByte di Boot ROM e a una memoria Flash

esterna collegata all’interfaccia SPI, che serve a memorizza-

re la configurazione dei motori di crittografia hardware RSA-

2048, SHA-256 e AES con chiave a 128, 192 o 256 bit. A bor-

do ci sono cinque canali di conversione A/D con risoluzione

di 10 bit, quattro timer programmabili e quattro modulatori

PWM programmabili mentre il package è Wfbga a 144 pin di

cui 116 sono GPIO.

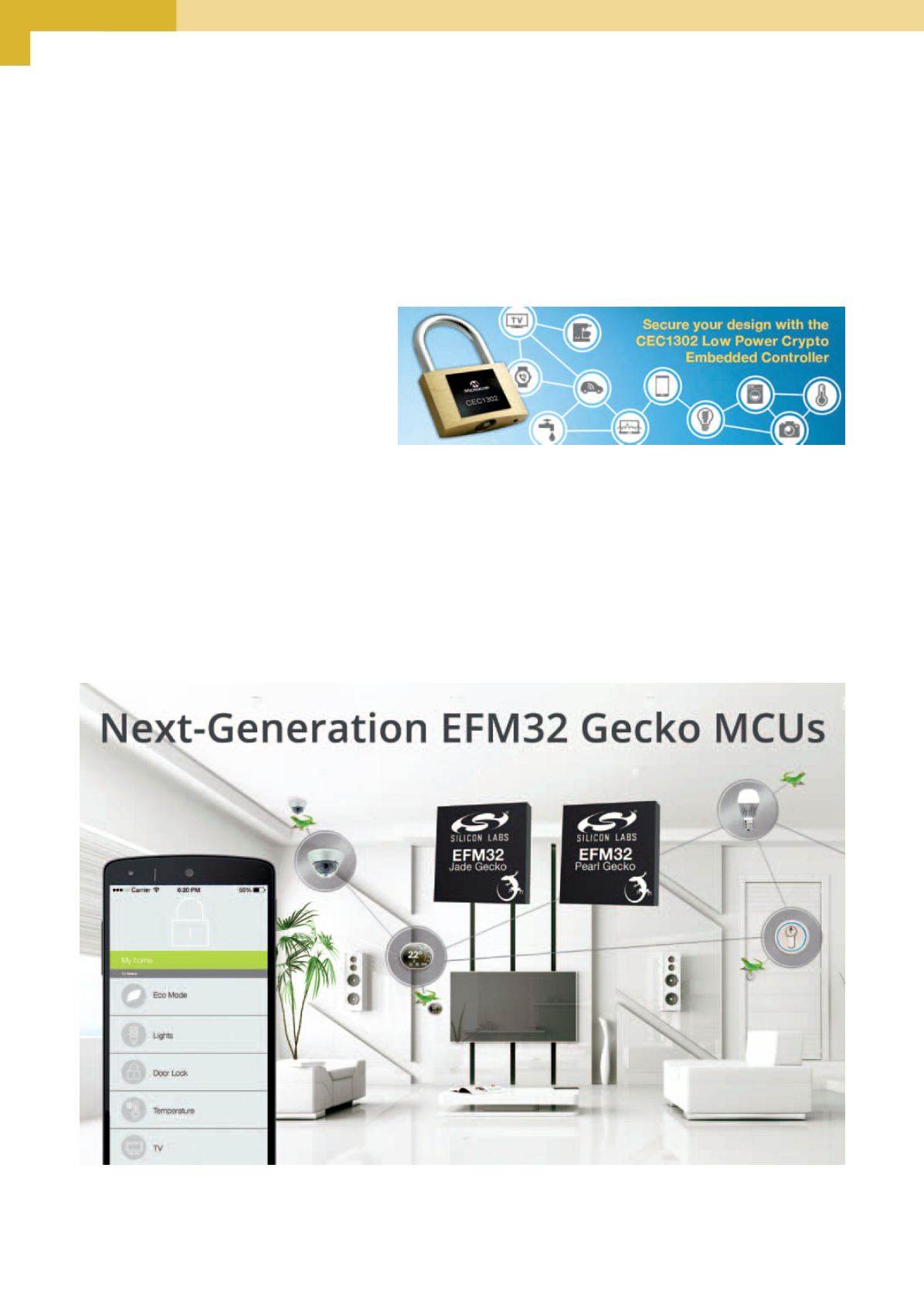

Fig. 3 – Sono ideali per le applicazioni wearable i nuovi EFM32 Gecko Silicon Labs che implementano solo core e periferiche di tipo Ultra-Low

Power fra cui un motore crittografico e un’interfaccia sensori

Fig. 2 – È pensato per la protezione delle applicazioni IoT il nuovo Microchip CEC1302

a 32 bit con i motori di crittografia hardware RSA-2048, SHA-256 e AES-128/192/256