eda/sw/T&M

IP ANALOGICA

74

- ELETTRONICA OGGI 445 - MAGGIO 2015

l’accuratezza di rappresentazione del segnale analogico. Questa

è la “risoluzione”. Maggiore è la risoluzione, più accurata sarà la

rappresentazione del segnale analogico originale. In altre parole,

la combinazione della frequenza di campionamento e del numero

di bit determina la qualità del segnale. Quando si progetta un SoC

per un’applicazione audio, bisogna cercare di ottenere la maggio-

re frequenza di campionamento (bit) possibile per raggiungere

unamaggiore sensibilità al rumore.Nelle tipiche applicazioni lega-

te alla sensoristica, una frequenza di campionamento di sei-sette

bit può invece essere sufficiente. Il numero effettivo di bit (ENOB) è

un indicatore completo per pesare le prestazioni complessiveA-D.

Questa metrica valuta quale sarà la qualità della conversione A-D

in un’applicazione reale, tenendo conto di fattori quali il rumore, la

temperatura e la natura dei segnali. In sostanza, il livello di ENOB

ideale vale quanto il numero di bit nell’ADC.

Architetture

Vi sono una varietà di tipi di architettu-

re ADC, ognuna con diverse frequenze

di campionamento, risoluzioni e livelli

di efficienza energetica. L’architettura

ad approssimazioni successive (SAR)

è oggi la più diffusa in quanto è molto

veloce e abbastanza scalabile. Un sin-

golo convertitore dati SAR può avere

frequenze di campionamento da 100

KSPS a 500 MSPS (con un’alta effi-

cienza energetica e una risoluzione di

medio livello, da 6 a 12 bit). Un conver-

titore SAR parallelo (come quello mo-

strato in Fig. 1) può vantare frequenze

di campionamento da 500 MSPS al 40

GSPS, pur garantendo con un livello

medio di efficienza e di risoluzione (da

6 a 12 bit). In confronto, l’architettura

ADC Flash offre velocità di campiona-

mento più elevate – da 100 MSPS a 40

GSPS – ma anche livelli più bassi di

efficienza energetica e di risoluzione

(3-6 bit). Un’altra popolare architettura

ADC, la sigma delta, offre alta risoluzio-

ne (da 10 a 24 bit) ma bassa frequen-

za di campionamento, da 10 SPS a 50

MSPS.

Nodi di processo: vantaggi

e sfide dei 28 nm

Mentre la maggior parte delle appli-

cazioni è attualmente basata sul nodo

di processo dei 65 nm, per i progetti

della prossima generazione vengono

ormai presi in considerazione i nodi più avanzati, da 28 nm in giù.

I 28 nm offrono molti vantaggi, ideali per le applicazioni mobili e

Internet of Things: maggiori velocità di commutazione dei transi-

stor, minore dissipazione di energia, dimensioni più contenute dei

chip, solo per citarne alcuni.

Al nodi di processo inferiori, invece, le problematiche di progetta-

zione aumentano. Le regole di disegno più complesse condizio-

nano le architetture IC. Tra gli effetti che si manifestano a 28nm

spiccano, per esempio, l’aumento degli accoppiamenti parassiti

e della resistenza delle interconnessioni, dei fori e delle vias. La

maggior interdipendenza intra-cella comporta notevoli problema-

tiche legate al rallentamento dei tempi e al leakage, soprattutto se

il progettista non tiene conto dello stress e degli effetti litografici

sul perimetro della cella. Altre problematiche riguardano l’elettro-

migrazione, l’impatto sulla resistenza parassita e sulla capacità a

O

ltre

250

blocchi

IP

analogici collaudati

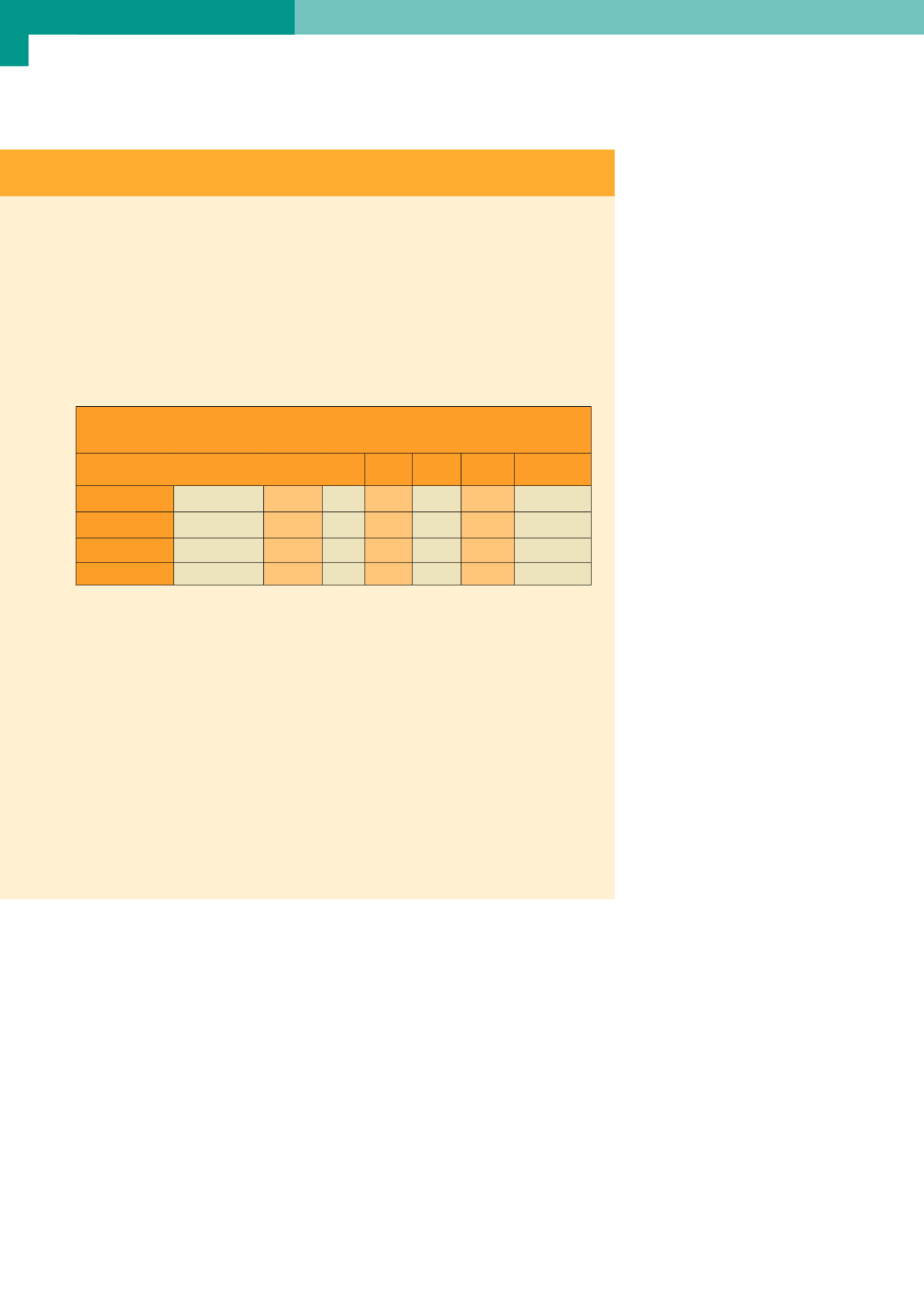

Cadence offre un portafoglio di oltre 250 prodotti IP analogici che soddisfano i requisiti

fondamentali e che possono essere facilmente integrati in una vasta gamma di progetti

SoC destinati a vari mercati, come ad esempio consumer, mobile, infrastruttura e indu-

stria. La tabella 1 riassume una panoramica delle offerte e dei nodi di processo supportati.

I prodotti possono essere raggruppati nelle seguenti categorie:

• AFE: AFE, ADC e DAC

• Temporizzazione: clock, ritardi, e phase-locked-loop

• Potenza: regolatori low-dropout (LDO) e regolatori lineari

• Monitor: sensori di temperatura

I nuovi prodotti di questa gamma sono dei blocchi IP di conversione dati, collaudati al

livello di silicio, che offrono alte prestazioni e consumi ridotti nei progetti a 28 nm.

Rispetto ad altre soluzioni IP sul mercato, questi blocchi di hard IP garantiscono tassi di

conversione fino a 10 volte superiori (3 GSPS), con consumi fino al 50% inferiori e aree

ridotte del 40%. Basati su un’architettura SAR parallela, i prodotti IP supportano applica-

zioni di nuova generazione, tra cui WiGig.

Sviluppati con livelli metallici bassi non restrittivi e basati su una macro analogica auto-

noma, i core possono essere facilmente integrati nei SoC. I core sono anche facilmente

collaudabili in quanto sfruttano un bus di prova analogico che garantisce l’accesso com-

pleto per la caratterizzazione e il test.

La famiglia di IP analogica Cadence da 28nm è composta da quattro soluzioni:

•

ADC e DAC doppi da 7-bit a 3 GSPS

•

ADC doppi da 11-bit a 1,5 GSPS

•

DAC doppi da 12-bit a 2 GSPS

Tabella 1 – Portafoglio di IP analogica Cadence

65 nm 40 nm 28 nm FinFET

Data Converter

ADC

DAC AFE:

•

•

•

In sviluppo

Sensore

Temperatura Tensione

•

•

•

In sviluppo

Timing

PLL

DLL Clock

•

•

•

In sviluppo

Alimentazione

LDO

POR

•

•

•