DIGITAL

SICUREZZA

50

- ELETTRONICA OGGI 445 - MAGGIO 2015

La prima colonna rappresenta una tipica

applicazione embedded. Se il dispositivo

embedded non è connesso a Internet - non

facendo parte di una rete - non c’è bisogno

di preoccuparsi degli algoritmi di cifratura,

della creazione di una connessione sicura o

della memorizzazione della chiave. Ci potreb-

be ancora essere motivo di prestare atten-

zione all’integrità del dispositivo - in partico-

lare se è importante proteggere la proprietà

intellettuale (IP). Impedire alla concorrenza

di leggere i contenuti di programma della

Flash interna protegge la proprietà intellet-

tuale di un’azienda da potenziali imitazioni.

Per questa protezione, cercate microcontrol-

lori che includano la protezione integrata da

lettura. Quando è richiesta la connettività a

Internet delle cose, è il momento di consi-

derare ulteriori funzioni per la sicurezza e

per la protezione del codice e dei dati. L’ag-

giunta di algoritmi per la sicurezza software

a un microcontrollore con funzione generi-

ca può fornire tutti i requisiti necessari per

l’invio sicuro di messaggi. È possibile usare

gli algoritmi software RSA o ECC per stabi-

lire una connessione sicura ed è possibile

avvalersi di una versione software dell’al-

goritmo AES per l’invio sicuro di messaggi.

Le chiavi sono memorizzate in una Flash o

in una RAM e sono spesso criptate usando

tecniche software. Un algoritmo AES via sof-

tware non è né più né meno sicuro di una

realizzazione dello stesso algoritmo acce-

lerata dall’hardware. La figura 2 evidenzia

anche i vantaggi legati alla sostituzione di

un microcontrollore con funzione generica

su cui girano algoritmi software con un di-

spositivo che include funzioni hardware per la sicurezza,

come la cifratura AES accelerata dall’hardware, la gene-

razione fisica di numeri casuali e opzioni più avanzate di

memorizzazione della chiave AES.

•

Il vantaggio principale di un blocco AES accelerato

dall’hardware rispetto a un’esecuzione software è il se-

guente: l’algoritmo AES accelerato dall’hardware è fino

a otto volte più veloce rispetto a una versione software.

Due vantaggi ulteriori sono i consumi inferiori e dimen-

sioni inferiori del codice di programma. Gli stessi algo-

ritmi software di cifratura AES possono girare in modo

più efficiente se traggono vantaggio dall’algoritmo AES

accelerato dall’hardware realizzato all’interno del micro-

controllore.

•

Un generatore fisico di numeri casuali (RNG) assicura

prestazioni migliori rispetto a una realizzazione software

per la creazione di chiavi realmente casuali. Quest’ulti-

mo sfrutta fenomeni fisici – come il rumore – per creare

numeri casuali, mentre le realizzazioni software devono

basarsi su un algoritmo per creare un numero casuale.

Un generatore fisico di numeri casuali è meno prevedibile

dispetto a una realizzazione software, e fornisce un grado

ulteriore di sicurezza.

•

Una funzionalità aggiuntiva per la sicurezza che si trova

in alcuni microcontrollori è la capacità di memorizzare

le chiavi AES in locazioni di memoria che sono leggibili

solo dai blocchi IP hardware. In questo modo le chiavi

non sono più esposte a un’estrazione software.

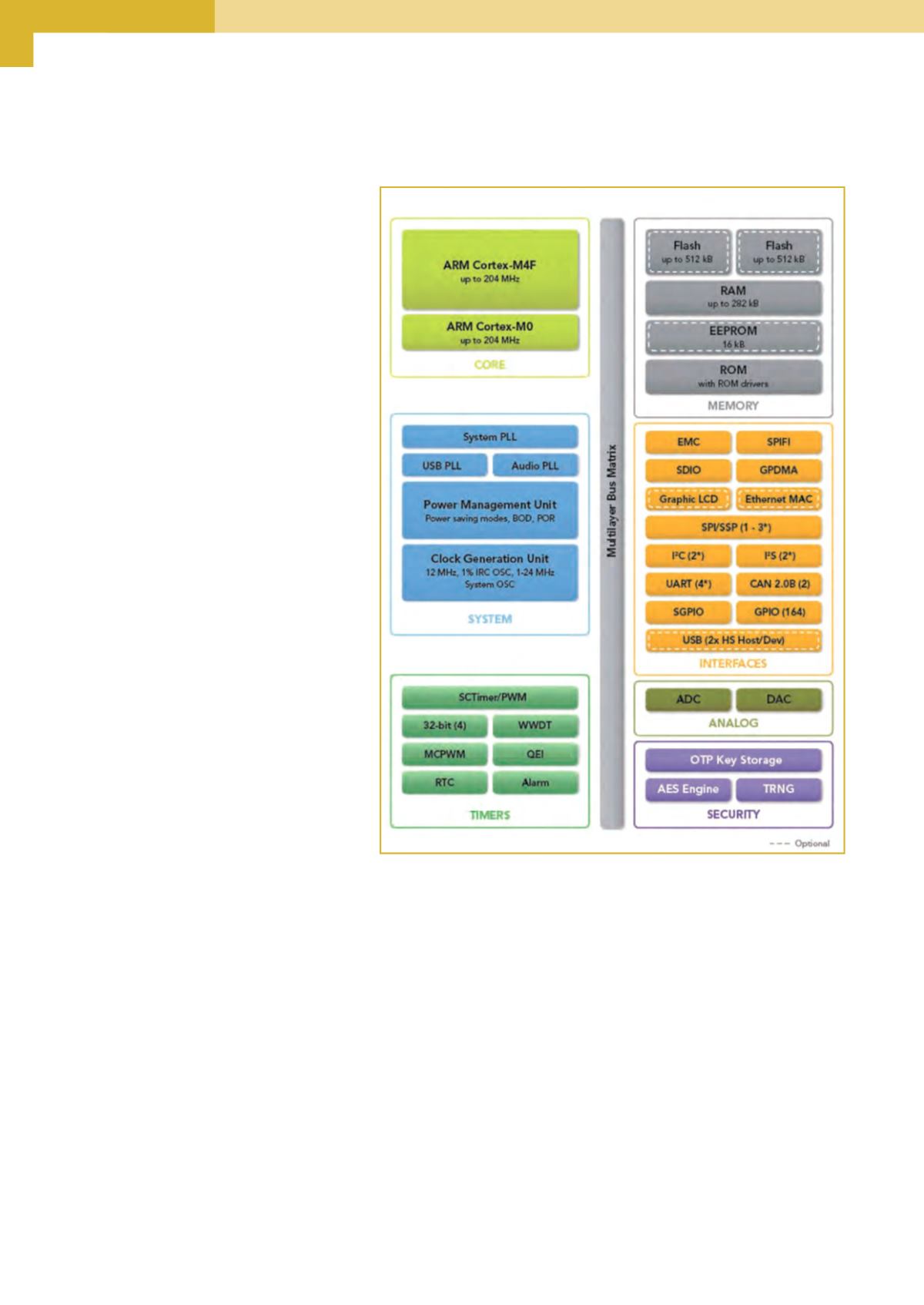

Fig. 3 – Diagramma a blocchi del dispositivo LPC43Sxx. LPC18Sxx offre funzionalità analo-

ghe a quelle di una unità Cortex-M3