POWER 5 - luglio/agosto 2014

XVI

Power

esempio, prima che la potenza arrivi nei circuiti inte-

grati sperimenta una caduta di tensione già nell’inter-

faccia fra chip e package. Tuttavia, oltre che in termini

statici, questo effetto è particolarmente significativo

nella sua componente dinamica dovuta all’influenza

degli elementi passivi tempo-varianti e specialmente

delle induttanze. In effetti, rispetto ai chip nei packa-

ge le componenti induttive sono più importanti per-

ché qui la componente più grande della caduta di

tensione è proprio determinata dall’induttanza intrin-

seca del package e risponde alla equazione V=L*di/

dt. In effetti, questa caduta di tensione introdotta dal

package può rappresentare dal 5% al 10 % di tutta la

caduta di tensione complessiva sui transistor. Come si

vede nell’equazione precedente la caduta di tensione

sul package dipende dalla sua induttanza intrinseca

ma anche dalla domanda di corrente (di/dt) e ciò

significa che non dipende solo dal package medesimo

ma da tutta la scheda PCB. Questo spiega l’importan-

za di considerare l’intero sistema quando si effettua

un’analisi dell’integrità della potenza.

Considerando l’analisi della caduta di tensione nel

dominio del tempo è stato già osservato che quando

numerosi transistor commutano contemporaneamen-

te si genera un aumento cumulativo dell’assorbimen-

to di corrente da parte del chip, il quale dev’essere

fornito dal package, dalla scheda PCB e infine dai

Voltage Regulator Module. Questi picchi di corren-

te sono di fatto una delle principali cause di malfun-

zionamento dei circuiti, specialmente nelle modalità

operative a elevata corrente, come durante i test di

Automatic Test Pattern Generation (ATPG), nei quali

si forzano a commutare insieme numerosi transistor

per collaudare più in fretta i circuiti e risparmiare

tempo e denaro sulle Automated Test Equipment

(ATE).

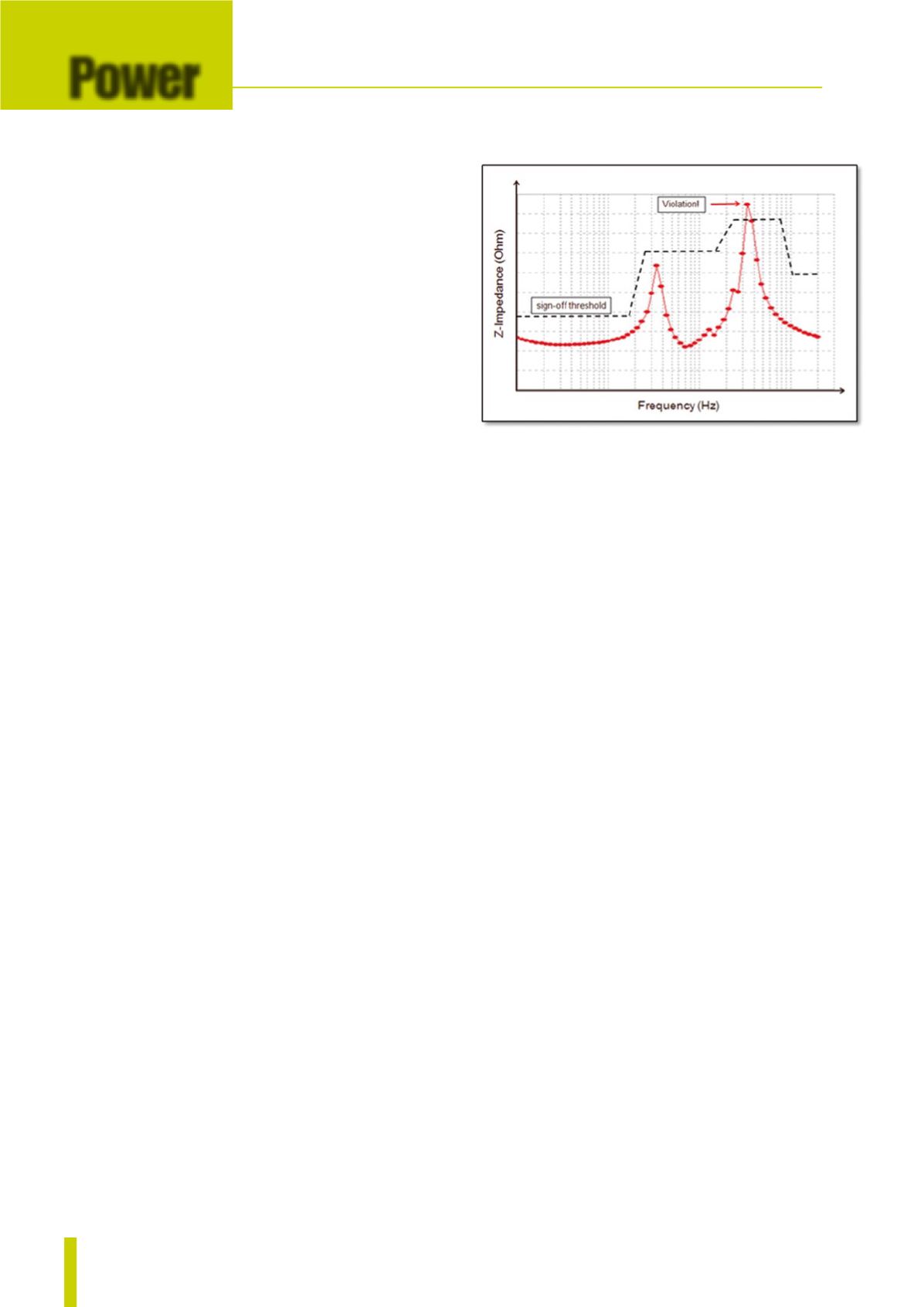

La Power Integrity a livello di sistema deve essere

anche affrontata nel dominio della frequenza, per-

ché l’impedenza è di fatto una variabile complessa

Z(

ω

)=R+(1/j

ω

L) e quindi varia in funzione della fre-

quenza. In ogni progetto è indispensabile assicurarsi

che l’impedenza della rete di distribuzione della po-

tenza rimanga entro i limiti imposti per le frequenze

operative del circuito.

Tipicamente, gli ingegneri verificano ciò rilevando

l’impedenza all’interfaccia fra chip e package laddo-

ve i package si connettono con i nodi C4 della rete di

redistribuzione (RDL). In generale, i chip e le PCB

sono più capacitivi rispetto ai package e, inoltre, i

package sono più induttivi rispetto all’induttanza in-

trinseca della rete di distribuzione della potenza sul-

la PCB. Considerando ciò la frequenza dei picchi di

impedenza (o picchi di risonanza) del sistema è in

gran parte determinata dalle risonanze LC fra chip e

package e fra package e PCB ed è determinata dall’e-

quazione f=1/(2

π√

LC).

Generalmente ci sono due principali picchi di riso-

nanza nel sistema chip-package-PCB.

A causa delle grandi dimensioni e dei numerosi con-

densatori sulla PCB l’accoppiamento fra i package e

la PCB determina il picco di frequenza più basso che

tipicamente si trova fra 10 e 500 MHz e dipende sia

dalla dimensione della scheda sia dalla capacità com-

plessiva presente. L’accoppiamento fra package e chip

determina il picco ad alta frequenza fra 1 e 5 GHz che

dipende in gran parte dall’induttanza dei package e

risponde alla stessa equazione f=1/(2

π√

LC) dove L e

C sono l’induttanza del package L

package

e la capacità

del chip C

die

.

Evitare i picchi di risonanza è fondamentale per la Po-

wer Integrity a livello di sistema. I progettisti di packa-

ge e PCB usano tecniche specifiche per disaccoppia-

re le capacità in modo da abbassare la frequenza dei

picchi e ridurne l’intensità. Oltre ad aggiungere le

capacità di disaccoppiamento per attenuare la fre-

quenza dei picchi d’impedenza, i progettisti devono

anche fare in modo di evitare che vi siano transistor

che commutano a frequenze vicine a quella dei picchi

di risonanza. Inoltre, determinare i picchi di risonan-

za associati ai singoli componenti del sistema (chip,

package o PCB) non è sufficiente perché ciascun

componente determina la frequenza e l’intensità del

picco d’impedenza con cui è risonante. Una soluzio-

ne più completa per l’analisi della PDN si può ottene-

Fig. 4 – Analisi dell’impedenza nel dominio della

frequenza a livello CPS. Il calcolo dell’impedenza e

delle posizioni ottimali delle capacità di disaccop-

piamento sono fatti con un simulatore elettroma-

gnetico ibrido e con un algoritmo di ottimizzazione