POWER 5 - luglio/agosto 2014

XVII

POWER INTEGRITY

re solo risolvendo a livello di Chip, Package & System

(CPS) includendo tutti insieme i modelli di potenza

dei circuiti integrati, i modelli dei package e i modelli

della PCB in un simulatore di campo elettromagneti-

co. La designazione dei picchi di impedenza è un pas-

so fondamentale nella verifica della Power Integrity

perché questi picchi costituiscono l’impedenza mas-

sima del sistema. La massima potenza è dimensionata

da un parametro noto come fattore di qualità Q che

può essere descritto in termini proporzionali come

Q~Imag[Z]/Real[Z] dove Z è l’impedenza dell’intero

sistema. Nella teoria degli oscillatori un elevato valore

di Q indica un basso tasso di energia che viene persa

durante le oscillazioni e perciò queste si attenuano

più lentamente. In pratica, Q è 2

π

volte il rapporto

fra l’energia totale accumulata e l’energia persa du-

rante ogni oscillazione o, in altre parole, il rapporto

fra l’energia immagazzinata e l’energia dissipata in

un periodo di oscillazione. Per un circuito RLC serie

ideale, che possiamo assumere per rappresentare una

rete di potenza chip-package-PCB, Q è definito come

Q=(

√

LC)/R e comprende gli effetti parassiti di tutti i

componenti del sistema.

In un sistema PDN, la resistenza e l’induttanza sono

in gran parte determinati dall’architettura della rete

disegnata per distribuire i segnali di potenza dai re-

golatori di tensione ai transistor attraverso percorsi

su più livelli, che mirano a evitare le congestioni e i

cortocircuiti. Ciò significa che è ben difficile inter-

venire sui percorsi della PDN per cercare di ridurre

l’induttanza o la resistenza e il progettista, similmen-

te all’ottimizzazione della frequenza dei picchi di ri-

sonanza, può solo aggiungere qualche capacità nel

chip, nel package o nella PCB per ottenere dei piccoli

effetti sui picchi di impedenza. Inoltre, la minimizza-

zione dei contributi di tutti i picchi di impedenza alla

risonanza del sistema CPS è critica perché influenza

direttamente il rumore elettromagnetico sui contatti

fra chip e package. Un simulatore di campo elettro-

magnetico ibrido può calcolare la Q sull’intero siste-

ma considerando anche le capacità di disaccoppia-

mento nel chip e nella scheda. D’altra parte, quando

la corrente di un dominio di potenza scorre proprio

alla sua frequenza di risonanza, si verifica un effetto

ad anello indesiderato perché il rumore di potenza

può amplificarsi esageratamente per brevi intervalli

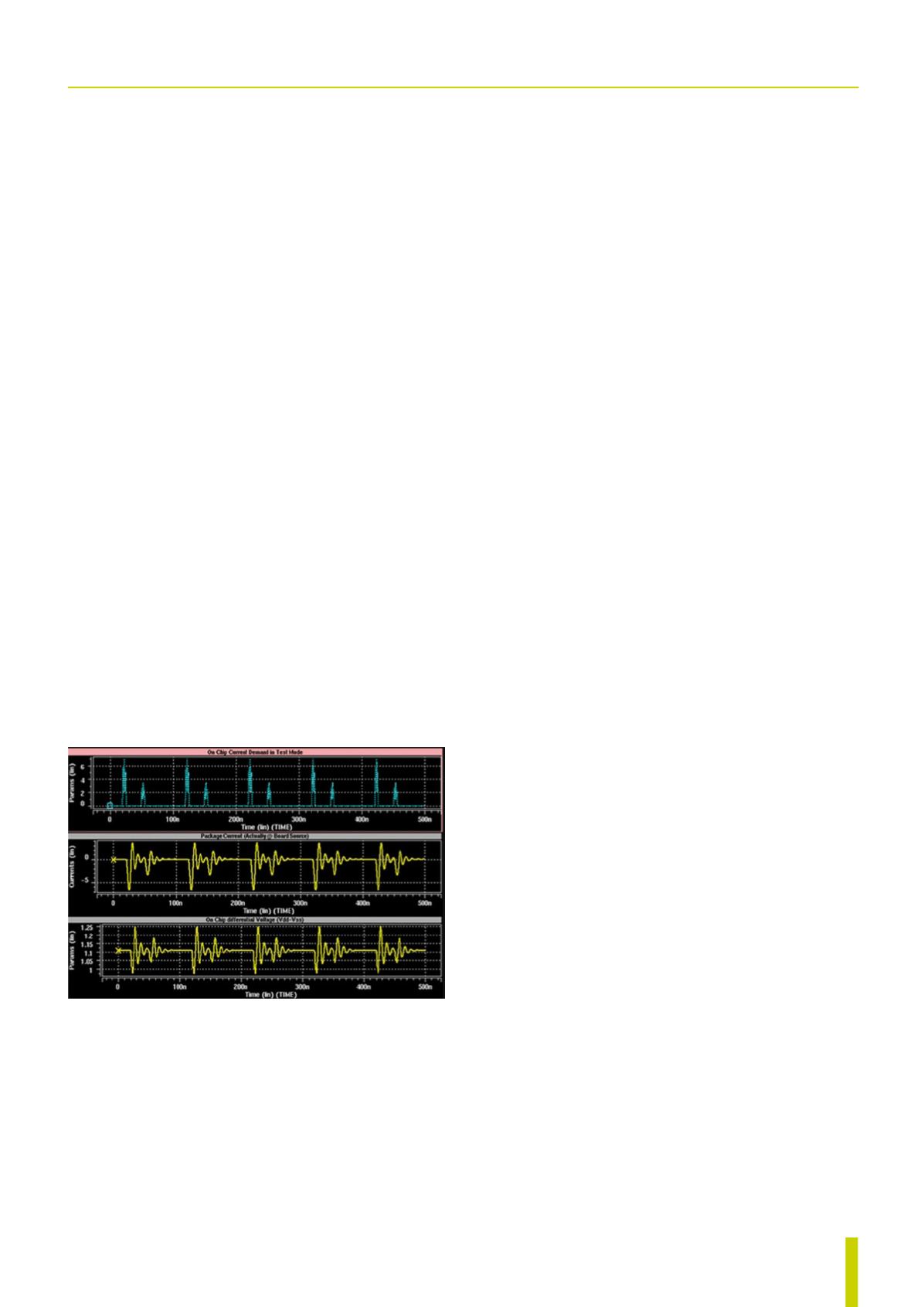

di tempo. Come si può vedere nella figura 5, il poten-

ziale di tensione (forma d’onda in basso) al contatto

C4 del circuito ha un andamento sinusoidale decre-

scente, nel quale l’intensità e il periodo dello smorza-

mento delle oscillazioni sono determinati dal fattore

di qualità del sistema.

Sopprimere le frequenza di risonanza è fondamentale

per garantire la Power Integrity. Tutti i circuiti sono

progettati per rispettare i limiti di rumore di tensio-

ne nelle condizioni operative normali, ma quando si

lavora in prossimità della frequenza di risonanza il ru-

more aumenta esageratamente causando malfunzio-

namenti. Nel precedente esempio, il rumore di ten-

sione appare come il 94% rispetto alla tensione ideale

riscontrabile con un’analisi sulla caduta di tensione a

livello di chip e, tuttavia, quando si aggiungono all’a-

nalisi anche i modelli del package e della scheda PCB,

allora si rilevano gli effetti di risonanza e la caduta di

tensione supera il 12% della tensione ideale. Eviden-

temente sono intervenuti dei picchi di tensione e cor-

rente che hanno amplificato gli effetti di risonanza.

In definitiva, numerosi fattori contribuiscono al ru-

more di potenza a livello di sistema. Chip, package e

PCB concorrono individualmente al rumore, ma sulla

qualità della Power Integrity intervengono svariati al-

tri fattori dovuti alla mutua interazione fra tutti i com-

ponenti del sistema. Questo appare evidente nell’ana-

lisi sulla caduta di tensione nel dominio del tempo,

nell’abbattimento dell’impedenza nel dominio della

frequenza e nella fase di ottimizzazione della frequen-

za di risonanza. In sintesi, la Power Integrity dev’es-

sere analizzata contestualmente sul sistema completo

per risolvere davvero tutte le complessità a livello di

sistema.

Fig. 5 – Esempio di simulazione nel dominio del tem-

po di un’analisi completa chip-package-PCB attorno

a una frequenza risonante. La forma d’onda in alto

rappresenta la domanda di corrente dei transistor

nel tempo, la forma d’onda intermedia è il flusso di

corrente dalla batteria fino al chip nel dominio del

tempo e, infine, la forma d’onda in basso rappresen-

ta il rumore di tensione osservato ai contatti. Si noti

l’esagerato effetto di amplificazione del rumore sui

contatti