POWER 5 - luglio/agosto 2014

XV

POWER INTEGRITY

aggiungono gli effetti di scarica e carica

delle capacità presenti in tutta le rete

di potenza nella stessa zona. La corren-

te richiesta dalla commutazione dinami-

ca dei transistor viene pertanto fornita

sia dall’energia accumulata dalle celle

vicine sia dal regolatore principale con

una conseguente caduta di tensione ge-

neralizzata sull’intero circuito integrato.

Inoltre, vanno considerati anche tutti gli

accoppiamenti tempo-varianti capacitivi e

induttivi che si producono nella rete PDN

e che invece vengono totalmente ignora-

ti dall’analisi statica degli IR Drop che si

effettua solo sulle resistenze. Invero, l’a-

nalisi dinamica sui transitori di potenza

coinvolge resistenze, capacità e indut-

tanze sia circuitali sia parassite presenti

nel chip e deve considerare le correnti

di commutazione necessarie in ciascu-

na cella. Le equazioni da applicare per

esprimere le cadute di tensione sono ben

note: V=I

2

R, V=L*di/dt e I=C*dv/dt. Una

volta che la rete è correttamente descrit-

ta con queste equazioni si può utilizzare

un software per la risoluzione circuitale

capace di tenere conto dei transitori per

determinare l’andamento tempo-variante

v(i) della tensione su ciascun transistor e applicare op-

portuni criteri d’interpretazione dei risultati.

Inoltre, la rete di distribuzione della potenza è connes-

sa al chip anche tramite i package e attraverso l’intera

scheda PCB e, dunque, per fare in modo che ciascun

chip riceva un’adeguata e stabile polarizzazione in ten-

sione sia i package sia la PCB sono progettati in

modo da minimizzare l’impedenza su tutta la

banda delle frequenze coinvolte. Oggi, l’esigen-

za di ridurre sia i costi sia i consumi di potenza

sta portando a una conseguente maggior com-

plessità del disegno delle PCB. Per esempio, per

ridurre il costo dei package si cerca di ridurre

al minimo il numero dei livelli implementati

al loro interno mentre le moderne tecniche di

progetto a basso consumo sono per lo più orien-

tate a creare domini multipli di aree circuitali

dove i blocchi a basse prestazioni sono alimen-

tati con tensioni più basse, in modo da limitare

i consumi e viceversa per i blocchi a elevate pre-

stazioni. A causa di questa tendenza i progettisti

si sono trovati a dover considerare nei circuiti

un gran numero di domini di potenza e perciò

hanno abbandonato i metodi di progettazione

tradizionali basati su sistemi di alimentazione

grandi e centralizzati, per preferire strutture gerarchi-

che che aumentano la complessità della PCB, perché

richiedono parecchi gruppi di connessioni distribuiti

su più livelli in tutti i domini di potenza.

Questa tendenza influisce inevitabilmente con l’au-

mento dell’impedenza nei package e nelle PCB e, per

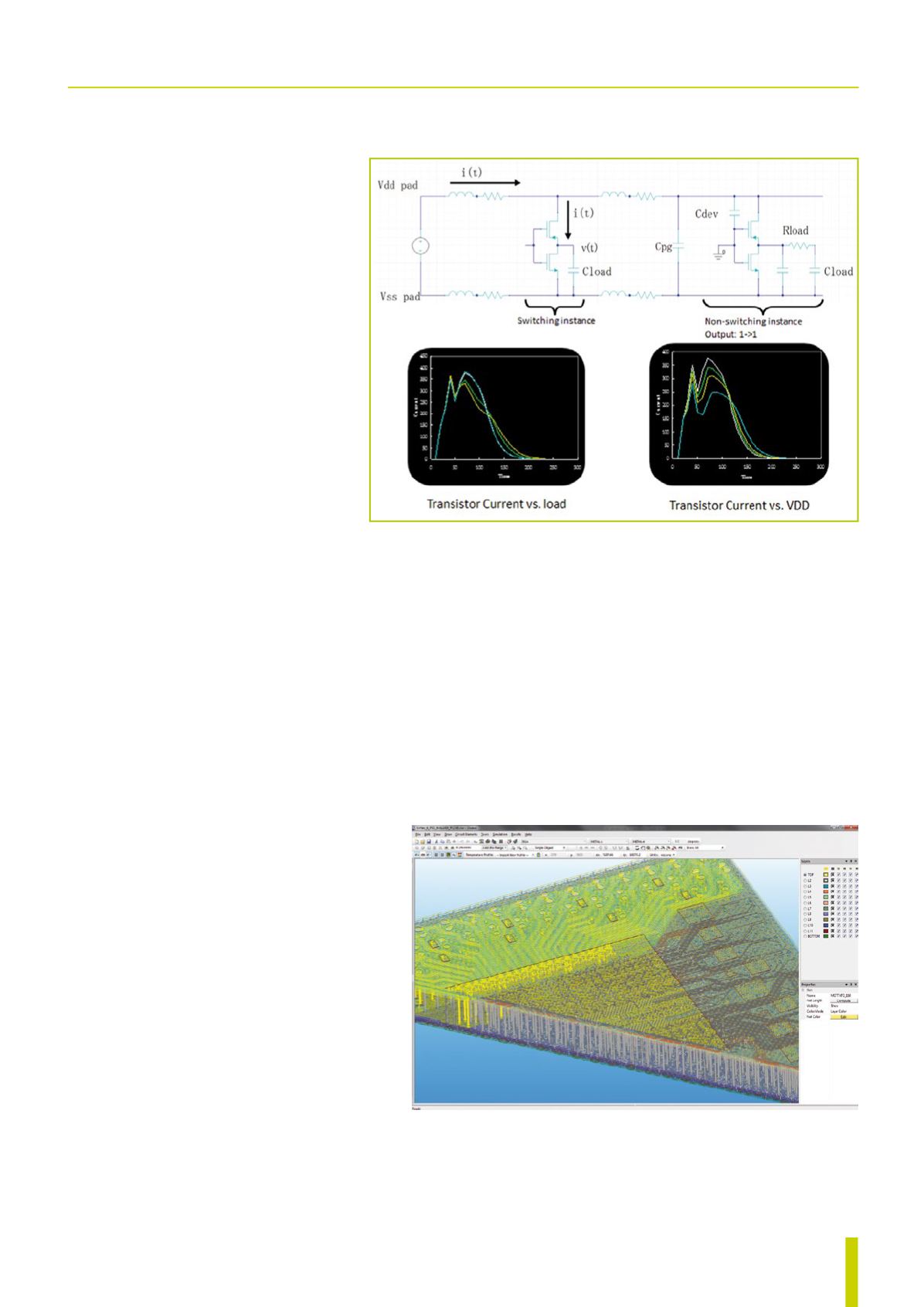

Fig. 2 – Modello per l’analisi dinamica della caduta di tensione. L’a-

limentazione è connessa al modello del chip nel quale i transistor

sono considerati come generatori di corrente tempo-varianti le cui

caratteristiche dipendono dal carico, dalla Vdd e dalla variabilità

dell’ingresso. La rete PDN è interamente modellata in termini di

componenti R, L e C, necessari per la simulazione dinamica e, inol-

tre, sono compresi anche tutti i componenti capacitivi di disaccop-

piamento

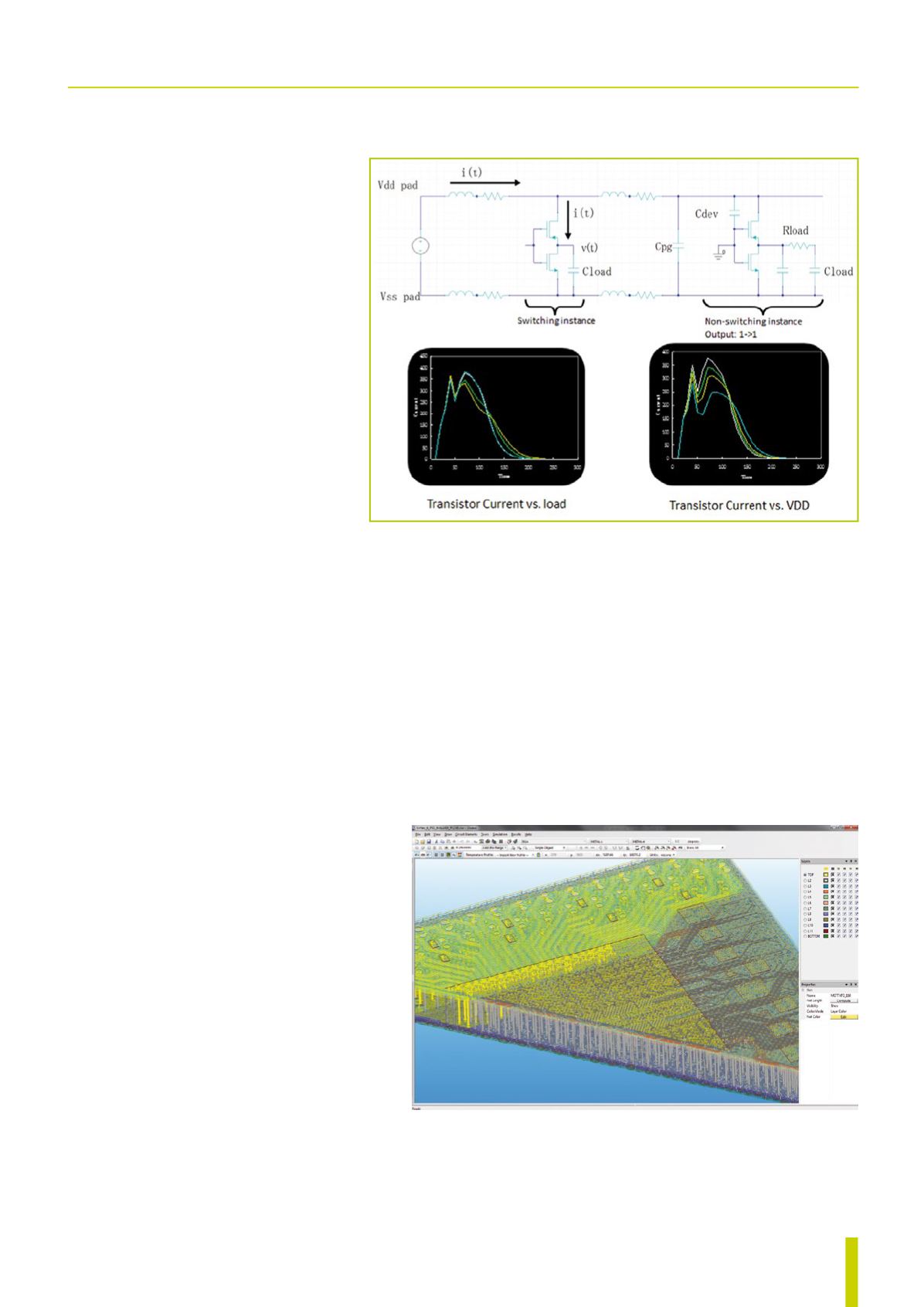

Fig. 3 – Esempio di layout di package a dodici strati. La com-

plessità dei circuiti integrati e i domini multipli di distribu-

zione della potenza concorrono a intricare la geometria e ad

aumentare l’impedenza dei package