37

EMBEDDED

65 • SETTEMBRE • 2017

ARCHITETTURE ETEROGENEE |

SPECIALE

tà nello stesso die insieme alle memorie piuttosto

;

;

@ %

questo occorre un’attenta modalità multi-thre-

ading capace di coordinare su ciascun core l’ese-

D

;

;

abbattere i tempi d’attesa.

Con questo approccio nascono i processori etero-

9

R D

minimo silicio.

/

K

J

9 D

-

processori dagli smartphone che ha spinto i core

9

9

^ ;

J

-

gomento di ricerca principale nei laboratori dei

protagonisti del silicio che mirano al Mobile He-

9

9 "F $@ 1

J

-

D

9 K J!

9

9 9 !

A NN

di istruzioni di partizionamento che consentono di

processare gli algoritmi scomponendoli in moduli

D

@ J!

À

R Á

D

9

autonomamente l’uno dall’altro con un’attenta

9

;

9 D

a opportune segnalazioni coordinate a un metali-

@

La Shared Virtual Memory implementa una

À

^

À

nell’assegnare e gestire la temporizzazione a tut-

9

in questo modo il parallelismo può adattarsi alle

esigenze di temporizzazione dei singoli core men-

Á

R

@

/

99

J! K

regole di comportamento a tutte le architetture

hardware e pur essendo originariamente nato per

%& 5%& ;

DSP e gli Fpga e oggi offre anche istruzioni per

tutti gli altri tipi di coprocessori con funzionalità

9

9 À

A

-

9

-

rici sia in tempo reale e tenere conto delle esigen-

D

@

Il consorzio Khronos ha recentemente rilasciato

! 2@2

D

NN

R À

9

9

-

;

@

/

À

; 9

-

9

9 K F 9

System Architecture (HSA) Foundation fondata

da AMD, ARM, Imagination, MediaTek, Qual-

comm e Samsung ma composta oggi da numerose

J&

7 9 @ 4 2 '

À ; F=4 @

;

F=4 @

2

9

-

R

-

nee guida standardizzate per unire sul silicio non

%&

GPU e DSP, ma anche gli Fpga, gli HPC (High-

Performance Computing) e qualsiasi altro blocco

IP o Asic possa far parte di un sistema eterogeneo.

Cluster multipli

Imagination Technologies

À

%& "/%=

/*

/'

*

threaded, multi-cluster e many-core heteroge-

neous perché consente di partizionare le risorse

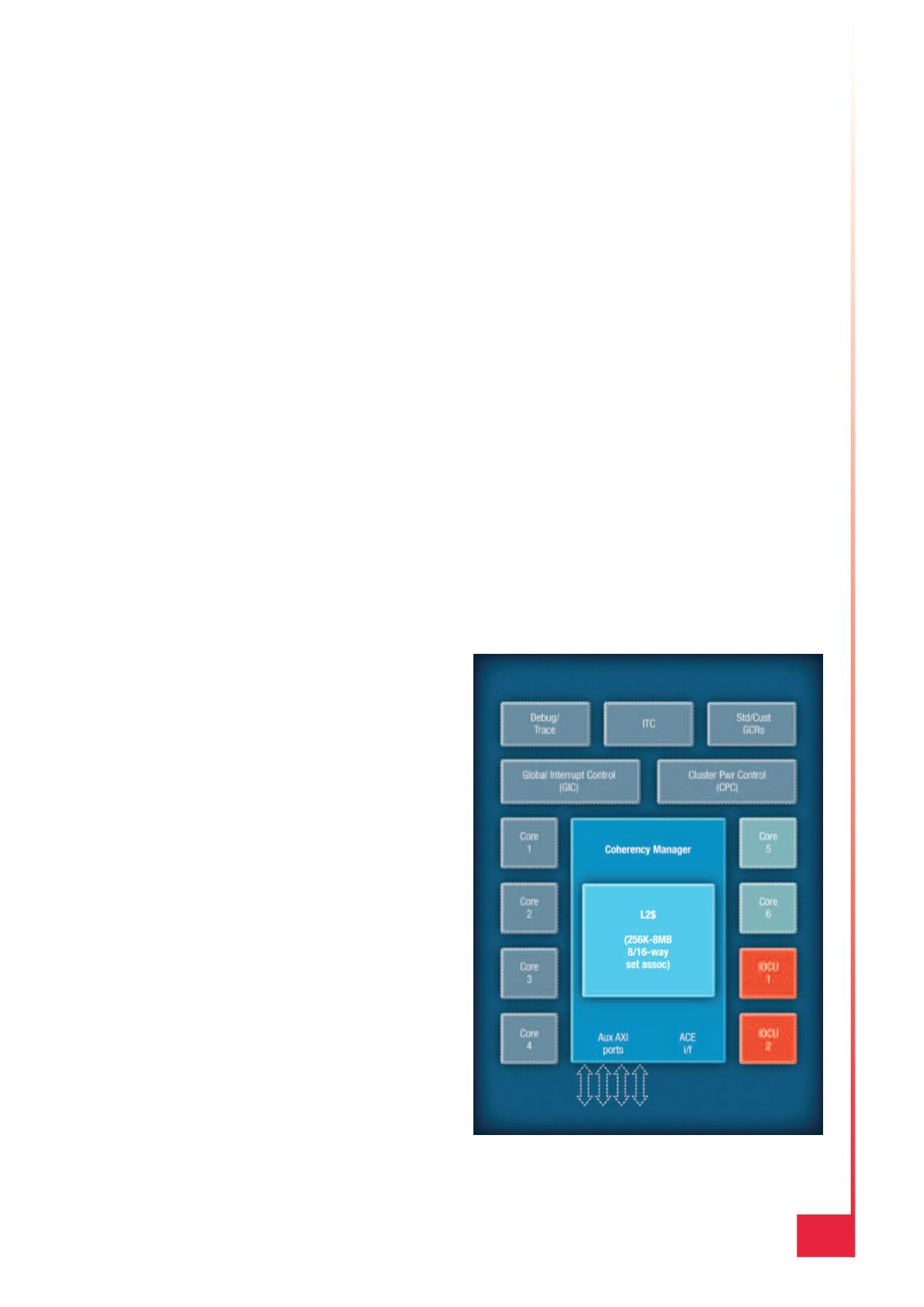

Fig. 2 – La MIPS Warrior I-class I6500 CPU di

Imagination Technologies consente di elaborare

fino a 64 cluster scomponendoli in 1536 porzioni

configurabili secondo necessità