63

EMBEDDED

61 • SETTEMBRE • 2016

INTERFACCE |

HARDWARE

Display Interface Converter CH7038/9 integra

due ricevitori e due trasmettitori differenziali

À

come DisplayPort 1.2 sia come eDP 1.3, un ricevi-

tore e un trasmettitore HDMI 1.4 compatibili con

À =8 4 /

-

titore LVDS a singolo o doppio canale da 18/24

bit e 165 Mpixel/s e persino un’uscita analogica

RGB VGA da 1900x1200 pixel. Il chip è in packa-

ge Lqfp da 176 pin o BGA da 196 e supporta sia in

À 7 1.1|7 44C/

DP/HDMI 2D con risoluzione di 1920x1200 pixel

a 60 Hz e DP/HDMI 3D con 1366x768 pixel a 120

Hz e, inoltre, include a bordo tre DAC con risolu-

zione di 9 bit, uno stadio audio I2S con due canali

in ingresso e otto in uscita e un’interfaccia audio

stereo SPDIF a 16 o 20 bit con velocità di cam-

pionamento di 192 kHz su due canali. Con que-

sto chip si possono risolvere la maggior parte dei

problemi d’interoperabilità fra differenti stan-

dard video e rispetto alla versione base CH7039,

nella versione CH7038 la risoluzione HDMI vie-

ne estesa a 4Kx2K con il supporto della funzione

Picture-in-Picture (PIP).

Parade Technologies

sviluppa chip a segnali mi-

sti e recentemente ha presentato un nuovo Timing

Controller realizzato appositamente per le speci-

À =@ 4 ;

-

sto nelle due versioni

DP691 da 2560x1700

pixel e DP693 da

1920x1200 pixel. En-

trambi questi Tcon han-

no a bordo un Integra-

ted Frame Buffer che

consente il Panel Self

Refresh parziale PSR2

sulle partizioni dei pan-

nelli e supportano la Di-

splay Stream Compres-

sion 1.1 e la Advanced

Link Power Manage-

ment prescritte da eDP

1.4b. La risoluzione

colori sulle immagini è

di 24 bit mentre la fun-

zione Smart-Backlight

provvede al controllo

dinamico della retroilluminazione. In entrambi

viene mantenuta la compatibilità con il preceden-

te standard eDP 1.3 ed entrambi non necessitano

del clock esterno grazie alla tecnologia CrystalFree

ma il package è Qfn da 5x12 mm e 76 pin per il

DP691 e da 5x10 mm con 66 pin per il DP693.

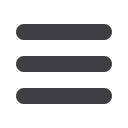

Toshiba

ha realizzato il Display Interface Brid-

ge TC358860XBG per risolvere l’interfacciamen-

to fra eDP 1.4 e le Display Serial Interface (DSI)

fornite dalla MIPI Alliance. Nel chip ci sono quat-

=@

À

-

dipendentemente l’una dall’altra alle velocità di

1,62, 2,16, 2,43, 2,7, 3,24, 4,32, 4,86 o 5,4 Gbit/s

per una velocità massima HBR2 sulle quattro li-

nee che corrisponde a 17,28 Gbit/s effettivi e poi

ci sono quattro linee DSI con velocità globale ef-

fettiva di 8 Gbit/s. La conversione avviene attra-

verso un motore di compressione dati 2-to-1 che

consente al chip di ricevere all’ingresso eDP un

segnale video 4K da 60 fps e trasformarlo in due

segnali DSI con formato 4K per la visualizzazio-

ne in altrettanti due display MIPI. Con i colori

standard RGB666 e RGB888 la velocità assoluta

in termini di pixel con risoluzione 4Kx2K è di 600

5 ` |

À

%*

C#F

F,

- 4 5 |

package è fBGA a 65 pin da 5x5 mm.

Fig. 5 – Toshiba Display Interface Bridge TC358860XBG consente di tra-

sformare i segnali video eDP 1.4 in segnali DSI per interfacce MIPI con

formato 4K e velocità di 600 Mpixel/s