EDA/SW/T&M

CO-DESIGN

78

- ELETTRONICA OGGI 439 - SETTEMBRE 2014

delle API per un componente che non è mai stato utilizzato. Se

l’ipotesi fatta non è quella corretta, è sempre disponibile un

datasheet completo (che può essere consultato nell’editor op-

pure richiamato semplicemente cliccando sul componente).

Una volta disponibile un progetto hardware completo, lo svi-

luppo firmware è supportato dal debugger integrato. Per il

collegamento del target è possibile utilizzare le tradizionali

interfacce JTAG o SWD. I kit di sviluppo di Cypress integrano

un chip di debug – si tratta ovviamente di un altro dispositivo

PSoC – che sostituisce la tradizionale sonda (probe) del de-

bugger. Per iniziare il debug è sufficiente collegare un cavo

USB. Nel caso l’utente utilizzi un proprio hardware è suffi-

ciente acquistare un’economica sonda per debug MiniProb3

che si collegata a una basetta (header) a 10 pin standard.

Tutte le API dei componenti sono fornite sotto forma di codice

sorgente in C così da semplificare il debug dell’interazione

tra hardware e software. Non è necessario includere alcuna

libreria e neppure effettuare ricerche

sul Web per reperire i driver del di-

spositivo. Inoltre non esiste restrizione

alcuna sul posizionamento dei bre-

akpoint o sulle porzioni di codice che è

possibile eseguire linea per linea (step-

through) durante il debug. Raramente

è richiesto il ricorso alla visualizzazio-

ne fornita da un assembler durante il

troubleshooting del comportamente di

un componente.

Al giorno d’oggi lo sviluppo è spesso

suddiviso tra i team hardware e sof-

tware: spesso i due team non sono

ubicati nella medesima sede o addirit-

tura sono dislocati in Paesi differenti.

Ciò potrebbe rappresentare un pro-

blema durante la selezione dei tool di

progetto, delle soluzioni di debug, dei

contratti di manutenzione e così via. Vi

sono elementi del flusso di ingegneriz-

zazione caratterizzati da un elevato livello di integrazione con

i sistemi aziendali, come ad esempio la gestione della docu-

mentazione o il controllo del codice sorgente. Per questo mo-

tivo il passaggio a un nuovo ambiente di sviluppo software

può risultare poco pratico.

In questi ambienti un approccio migliore è considerare PSoC

Creator come un tool per la configurazione del chip piuttosto

di un IDE da utilizzare in sostituzione di analoghi ambienti.

Gli sviluppatori hardware possono utilizzare questo tool per

generare un progetto, tutti i dati di configurazione e le API. I

team software, dal canto loro, devono semplicemente inte-

grare questi file negli IDE di loro scelta e seguire il classico ci-

clo edit-build-debug. Il team di sviluppo hardware può utiliz-

zare PSoC Creator per realizzare test bench per i loro progetti

e le schede sulle quali vengono utilizzati. È anche possibile

create BSP (Board Support Package) o HAL (Hardware Ab-

straction Layer) da condividere con il team software in modo

da rendere l’interazione con il dispositivo tanto più semplice

ed esente da errori possibile.

La consegna di una nuova scheda agli sviluppatori softwa-

re è un processo molto problematico. Per cercare di atte-

nuarne gli effetti PSoC Creator prevede una funzionalità che

permette di generare un datasheet per il progetto PSoC. Le

informazioni di configurazione del dispositivo, il setup del

clock, le selezioni dei pin e le descrizioni di tutte le API dei

componenti generati possono essere resi disponibili in un

unico file che contiene il datasheet, direttamente dal tool. Il

rischio di errori è escluso in quanto il documento è genera-

to dalla macchina.

Q

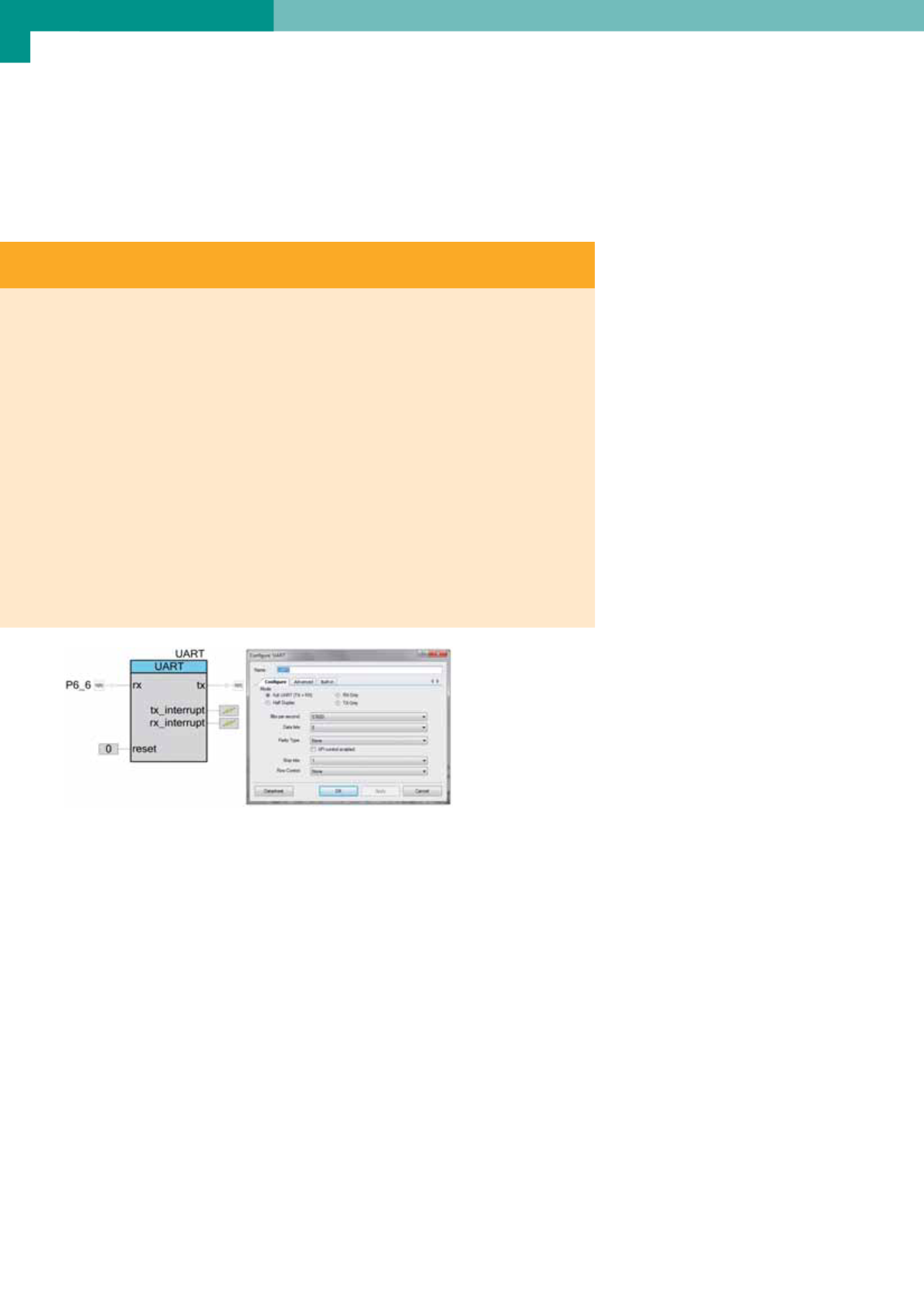

Fig. 2 – Configurazione di un UART: tutte le opzioni sono riferite alla

funzione e non all’implementazione della periferica

D

ISPOSITIVI PROGRAMMABILI DI NUOVA GENERAZIONE

La linea PSoC di Cypress Semiconductor è composta da dispositivi programmabili di

nuova concezionebasati sul coreCortex-Mchemettono adisposizioneun’ampiagamma

di opzioni in termini di CPU, velocità e funzioni, non richiedono agli utenti di integrare

blocchi IP, di preoccuparsi delle interfacce verso i bus o sviluppare il codice di boot.

Poiché l’hardware è completamente programmabile, è possibile ottenere prestazioni

simili a quelle di un circuito ASIC, consumi ridotti e prezzi competitivi, oltre all’accesso a

dispositivi già pronti per la produzione che possono essere modificati (riprogrammati)

finché non sono pronti per la spedizione ai clienti. Senza dimenticare che essi integrano

funzioni analogiche, convertitori A/D, comparatori e amplificatori, che solitamente non

fanno parte del corredo degli FPGA. In considerazione dei vantaggi appena descritti, è

logico domandarsi quale sia l’ostacolo che impedisce l’adozione su larga scala di questi

dispositivi al posto di integrati custom o di FPGA caratterizzati da elevati consumi.

La risposta è relativamente semplice. L’ostacolo è rappresentato dal software. Al fine di

sfruttare al meglio le potenzialità di questi dispositivi i progettisti devono disporre di

tool che integrano le risorse hardware e software necessarie senza costringere nessun

membro del teamdi sviluppo a utilizzare un singolo IDE di natura monolitica.