50

- ELETTRONICA OGGI 437 - GIUGNO 2014

DIGITAL

20 nm

(in uscita) sul lato PCI Express deve stare al passo con la

velocità di trasmissione dati (in ingresso) sul lato Ethernet.

Per schede di in interfaccia di rete di tipo 100G, sono

richiesti più blocchi integrati di tipo PCIe Gen3. Gli FPGA

Kintex UltraScale sono in grado di assicurare i requisiti

di questa applicazione a fronte di costi e di consumi più

bassi rispetto ai componenti Virtex-7 XT con blocchi x8

Gen3 integrati. I dispositivi KIntex UltraScale sono dotati

di più blocchi PCI Express Gen3 integrati, oltre ad un’unità

MAC di tipo 100G Ethernet, che nei dispositivi della serie

7 era disponibile sotto forma di core IP sintetizzabile. La

realizzazione di una scheda di interfaccia di rete in un

dispositivo UltraScale Kintex non solo consente di mettere

a punto la soluzione in un dispositivo di fascia intermedia,

ma libera anche risorse logiche per funzioni aggiuntive

di elaborazione dei pacchetti in grado di differenziare il

prodotto finale.

Le applicazioni nelle comunicazioni wireless

Nell’industria delle apparecchiature per le comunicazio-

ni wireless, i principali produttori stanno introducendo

soluzioni avanzate di tipo LTE e LTE Advanced, mentre

stanno iniziando a sviluppare nuovi sistemi basati su

architetture sofisticate che supportano funzionalità mul-

titrasmissione, multiricezione e di beamforming. L’ultima

generazione dei sistemi di tipo LTE e LTE Advanced, che

si basavano comunemente su architetture costituite da

due FPGA Virtex-7 X690T, in grado di offrire una combi-

nazione di risorse DSP e BRAM elevate, con i dispositivi

Kintex Ultrascale ora possono offrire una soluzione equi-

valente a costi inferiori basata su un singolo dispositivo.

L’FPGA Kintex Ultrascale offre il 40 % in più di blocchi

DSP in un dispositivo di fascia intermedia. Dispone inol-

tre di una funzione di allineamento a monte del somma-

tore e di ulteriori percorsi di controllo dell’accumulatore,

che consentono di ottenere un’efficienza migliore della

funzione DSP48, l’aggiunta di ulteriori equazioni ed un

calcolo più efficiente. Questo significa che in un disposi-

tivo UltraScale, un’applicazione di tipo Virtex a due chip

può essere ridotta ad una soluzione basata su un singolo

componente Kintex KU115 per l’elaborazione a 48 canali.

L’FPGA Kintex UltraScale KU115 ha 5.520 blocchi DSP

e 2.160 blocchi BRAM. IN più, la Design Suite Vivado

di Xilinx presenta un tool di sintesi all’avanguardia, che

Xilinx ha co-ottimizzato, per aiutare gli utenti a realizzare

in modo efficiente algoritmi complessi con funzioni di

beam forming e altre applicazioni ad alta intensità di

calcolo.

Q

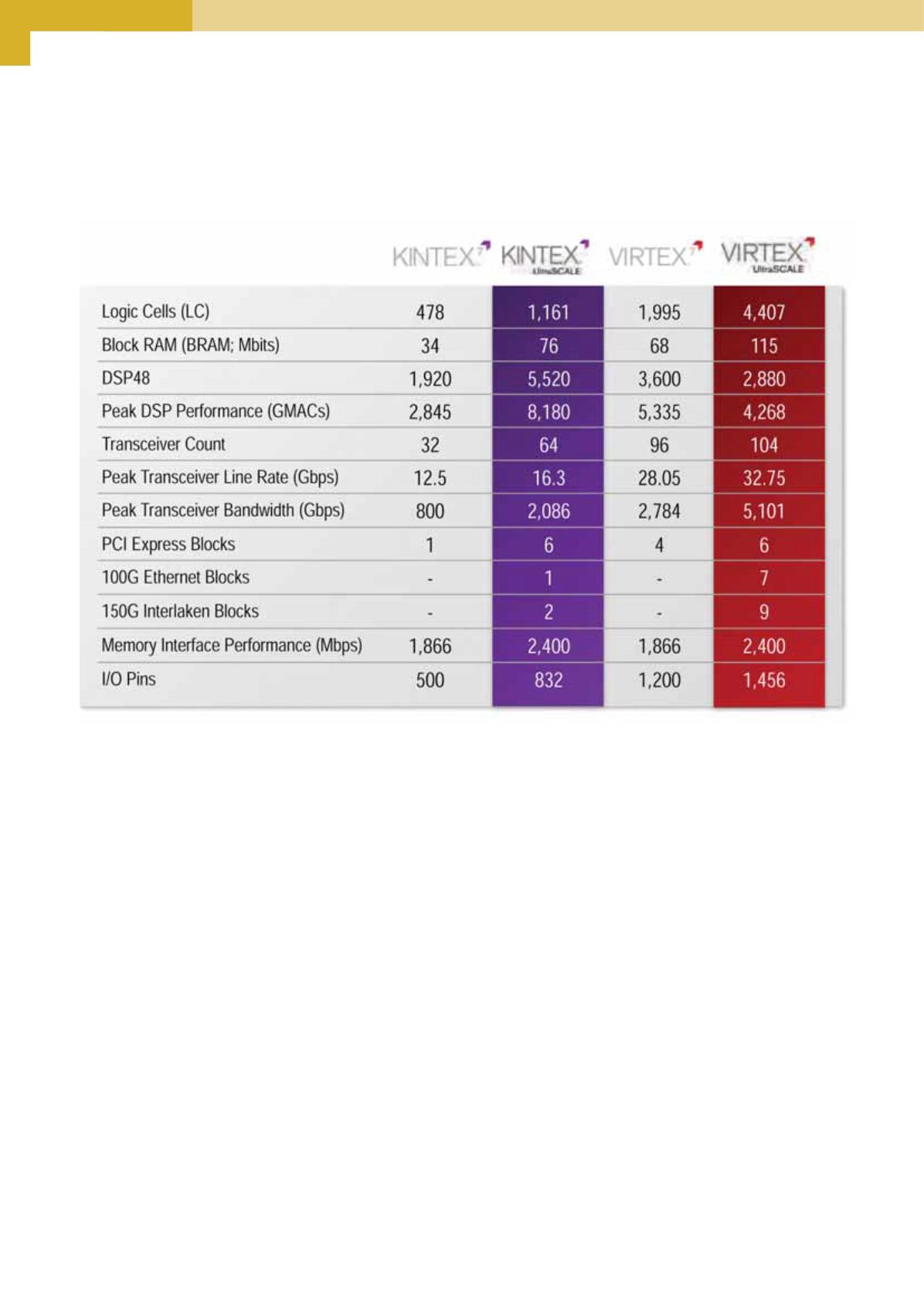

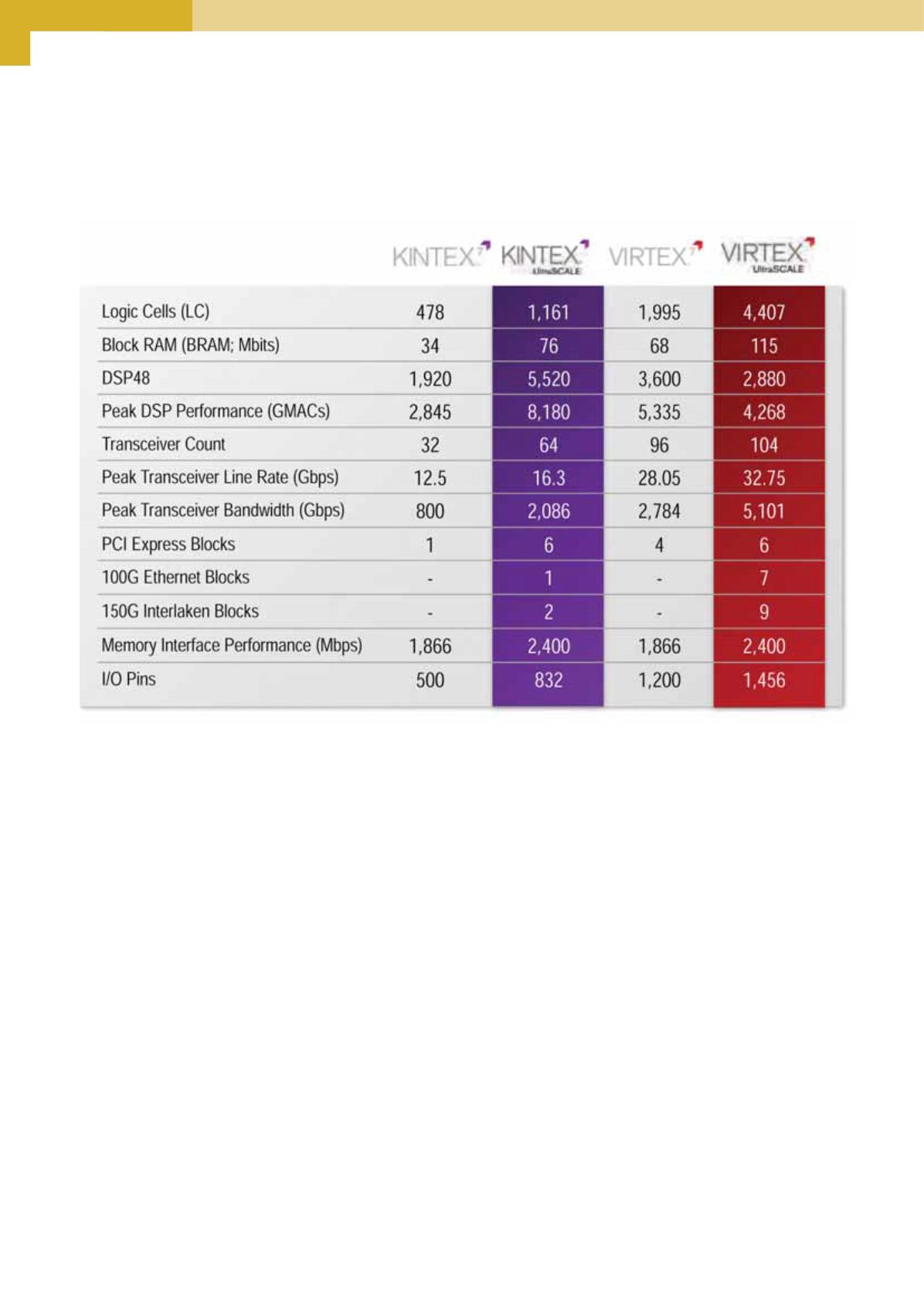

Tab. 1 – Principali prestazioni degli FPGA Kintex e Virtex

UltraScale da 20 nm