51

- ELETTRONICA OGGI 437 - GIUGNO 2014

DIGITAL

HYBRID MEMORY

Come implementare

in maniera efficiente

gli algoritmi di cifratura

L

a crittografia è divenuta una tecnologia indispen-

sabile per assicurare un trasferimento sicuro

e protetto dei dati dalla fonte alla destinazione.

Le tecniche crittografiche più comuni utilizzano un

algoritmo deterministico con una trasformazione inva-

riabile che opera su blocchi di dati di lunghezza fissa.

Advanced Encryption Standard (AES), Data Encryption

Standard (DES), International Data Encryption Algorithm

(IDEA) e Rivest Cipher (RC5) sono alcuni esempi.

Un approccio di questo tipo, che prevede la cifratura

a blocchi (block cipher), pone alcuni vincoli in termini

di throughput, elaborazione dati e capacità di buffering

dell’hardware in quanto la cifratura deve essere eseguita

prima dell’arrivo del successivo blocco di dati (chunk).

Un numero rilevante di sistemi di cifratura industriali

supporta velocità di trasferimento dati superiori a 200

Mbps ma l’hardware richiesto per garantire prestazioni

di questo tipo è solitamente un circuito ASIC, il cui costo

è decisamente maggiore rispetto a quello di un semplice

microcontrollore.

Sebbene sia possibile implementare la cifratura su una

MCU a 8 bit con una memoria esterna, come ad esem-

pio un microcontrollore 8051, il tempo necessario per

eseguire l’operazione di cifratura è di un ordine di gran-

dezza superiore rispetto a quello richiesto da un ASIC.

Nel corso dell’articolo è spiegato come un SoC con lo-

gica programmabile possa utilizzare il core della MCU

abbinato a opportune funzionalità hardware come UDB

(Universal Digital Block) e DMA (Direct Memory Access)

per implementare in maniera efficace l’operazione di ci-

fratura e migliorare la temporizzazione complessiva del

sistema.

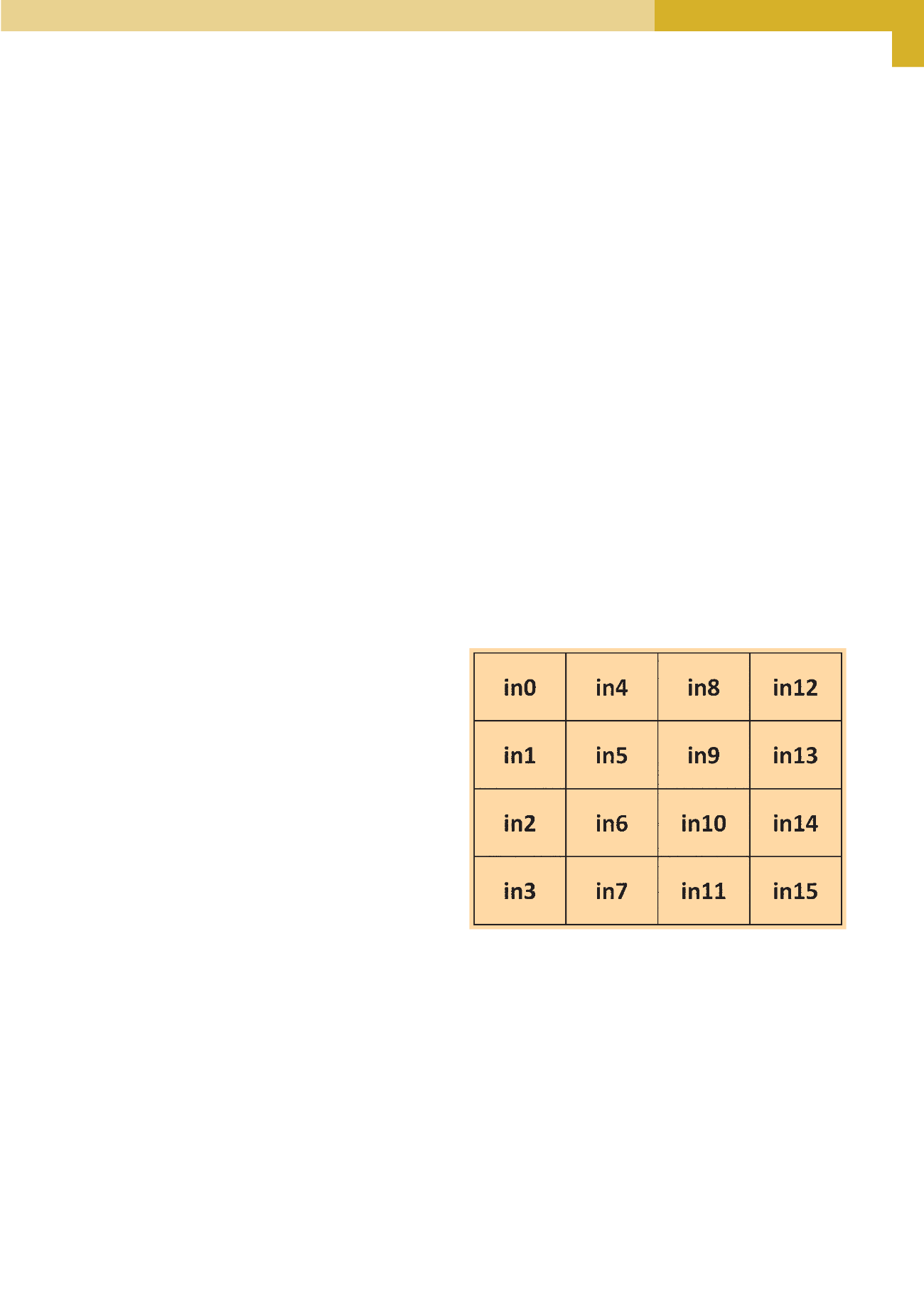

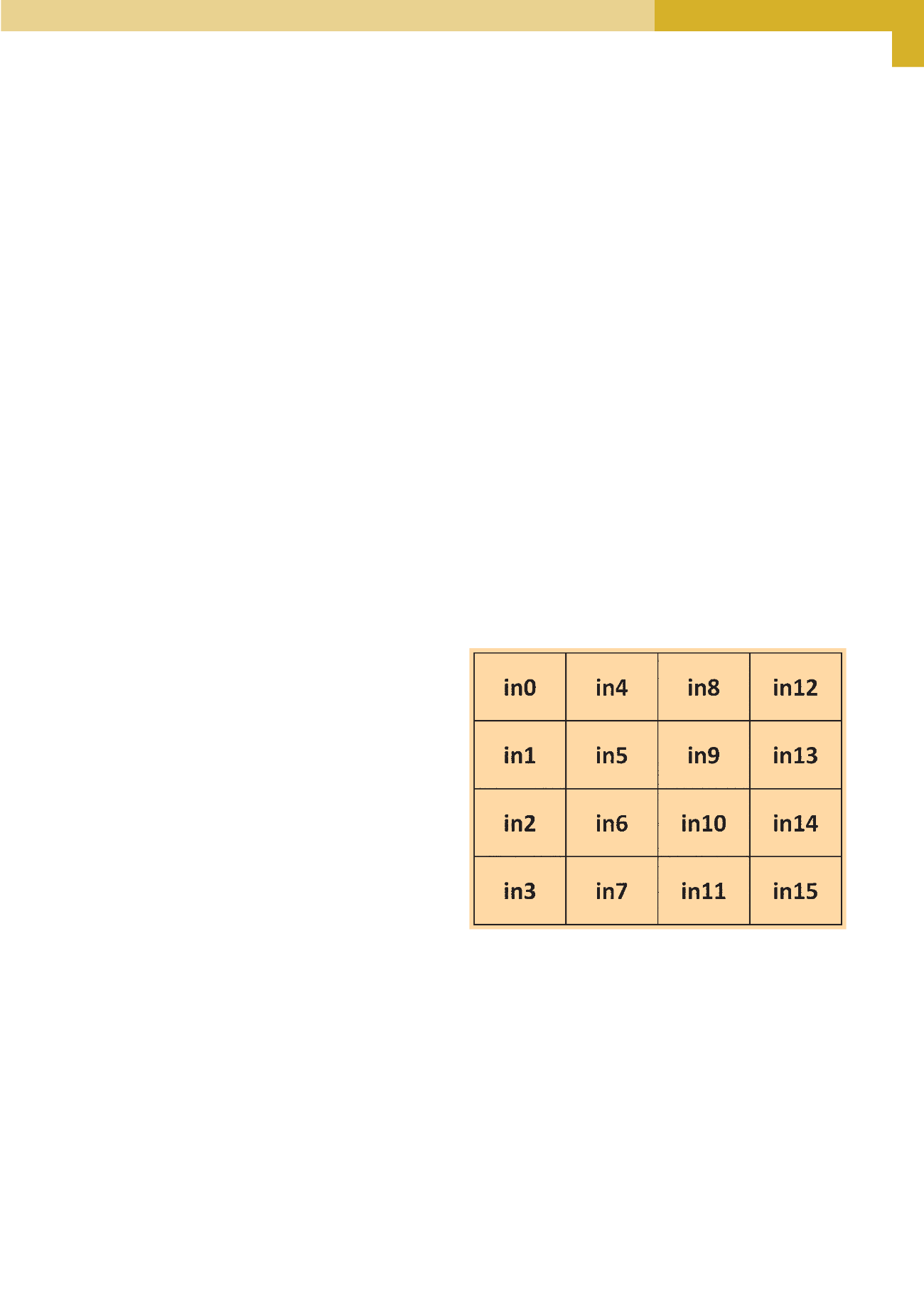

AES, sicuramente una delle tecniche di cifratura a bloc-

chi di uso più comune, implementa la crittografia a

chiave simmetrica. Come esempio si utilizzerà AES-128

che opera su un blocco di 16 byte (128 bit, appunto) di

dati elaborati mediante una chiave di cifratura a 128 bit

Ahmed Majeed Khan

Engineer

Cypress Semiconductor

Asma Afzal

Engineer

Cypress Semiconducto

r

Khawar Khurshid

Ph.D

Director of NUST-Cypress joint

Research center - Islamabad

Con un dispositivo PSoC abbinato a

opportune funzionalità hardware è

possibile implementare in maniera efficace

le operazioni di cifratura e migliorare la

temporizzazione complessiva del sistema

Fig. 1 – Con un motore LoadSense è possibile selezionare un margine

di sicurezza minore, poiché la coppia è nota e gestita