43

- ELETTRONICA OGGI 437 - GIUGNO 2014

DIGITAL

20 nm

Steve Leibson, Xcell Daily Blog, Xilinx

Un fenomeno che si è verificato tempo fa nel mondo degli

ASIC sta ora interessando il settore degli FPGA. Il fenomeno

in questione è la prevalenza del ritardo di segnale nelle de-

terminazionedelleprestazioni a livellodi progetto. Nel corso

degli anni, lo scalingDennardha prodottoun aumentodella

velocità dei transistor, mentre la legge di Moore sullo sca-

ling ha fatto crescere la densità dei transistor per millime-

tro quadro. Purtroppo, per le interconnessioni queste leggi

funzionano al contrario. Al diventare più sottili e più piatte

in virtù della Legge di Moore, esse diventano più lente. In

ultima analisi, il ritardo dei transistor di-

venta insignificante e il ritardo dei segnali

domina. Lo stesso problema si è presen-

tato con l’aumento della densità degli

FPGA e con l’introduzione dei dispositivi

interamente programmabili UltraScale di

Xilinx nell’ambito della progettazione di

classe ASIC. I dispositivi UltraScale sono

stati re-ingegnerizzati per ovviare a que-

sto problema, intervenendo su tre fronti:

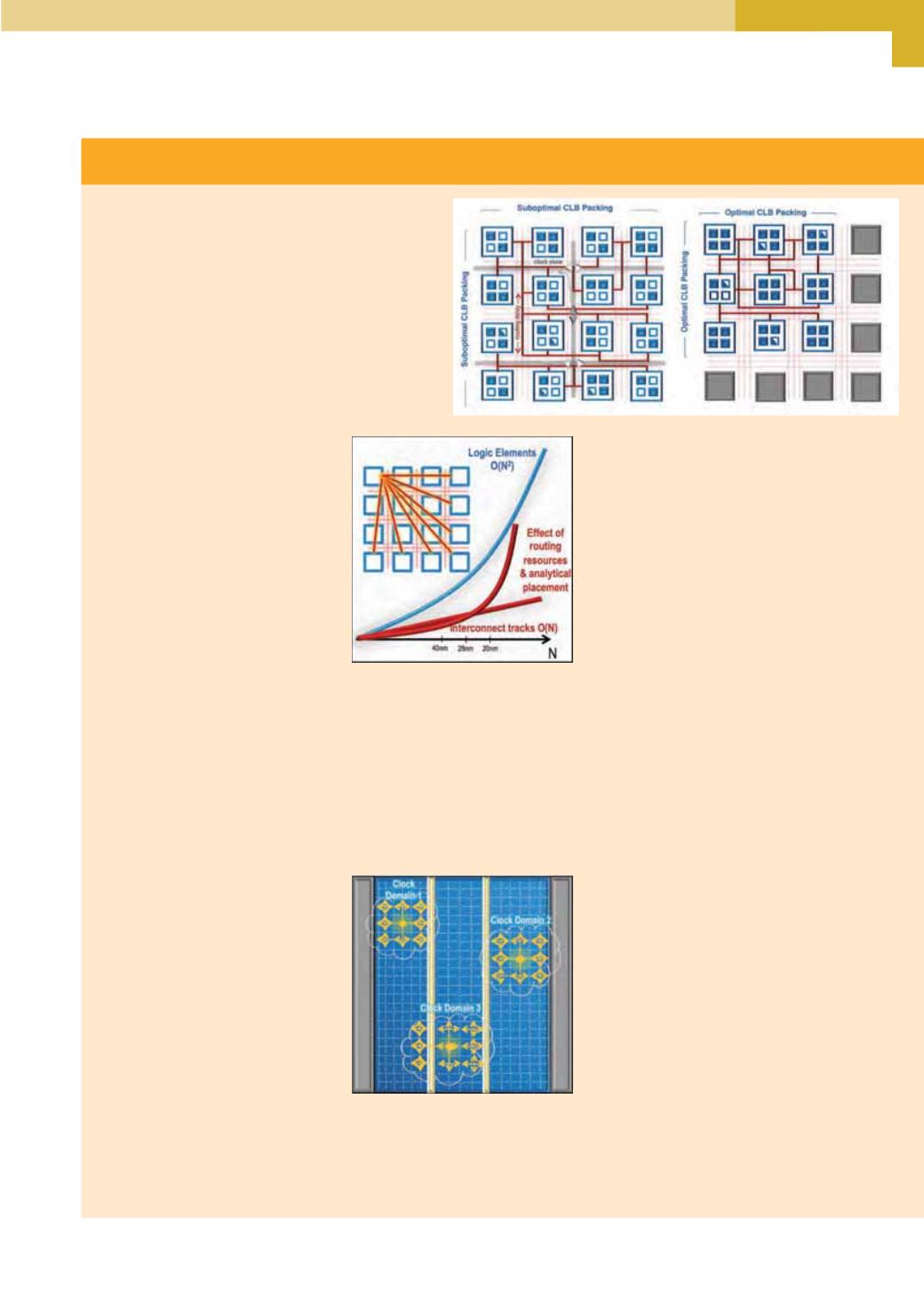

1) I blocchi sono stati compattati, di modo

che i segnali non debbano compiere lun-

ghi percorsi. Di conseguenza, i blocchi lo-

gici sono più densamente integrati e sono

richieste meno risorse di instradamento

segnali fra un blocco logico configurabile

e l’altro. I percorsi dei segnali diventano

inoltre più corti. Le modifiche apportate

ai blocchi logici configurabili (CLB) dell’ar-

chitettura UltraScale includono l’aggiunta

di ingressi e di uscite dedicate a ogni flip-

flop all’interno del singolo blocco CLB (di

modo che i flip flop possano essere usati

in modo indipendente), l’aggiunta di più

segnali di abilitazionedel clock dei flipflop

e l’aggiunta di clock separati ai registri a

scorrimento e di componenti RAM distri-

buiti.

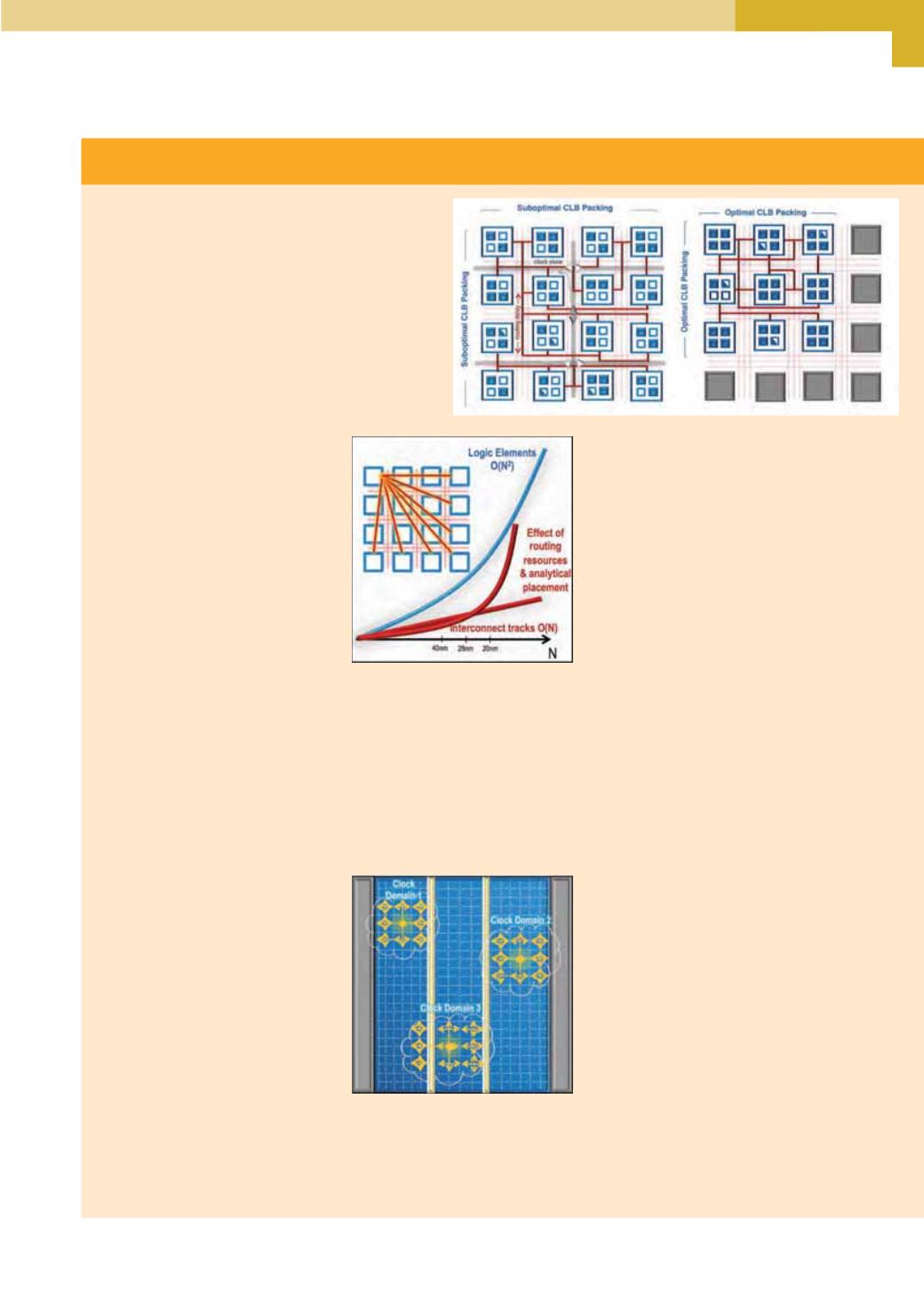

2) Sono state aggiunte più risorse di in-

stradamento segnali. Un aumento nella

densità dei transistor in base alla Legge

di Moore produce un aumento dei CLB

proporzionale a N2 in cui N è il fattore li-

neare di scala del processo tecnologico

IC. Purtroppo, le risorse di instradamento

segnali nell’FPGA tendono a scalare line-

armente con N, molto più lentamente.

Per l’architettura UltraScale, la soluzione

a questo problema ha richiesto l’aggiunta

di più risorse locali di instradamento dei

segnali, di modo che l’instradabilità dei

segnali migliori più rapidamente con l’au-

mento della densità di blocchi CLB. La fi-

gura 2R mostra il risultato. Tuttavia, non

è sufficiente aumentare semplicemente

le risorse hardware di instradamento dei

segnali. Occorre anche migliorare gli al-

goritmi di piazzamento e instradamento

dei segnali del tool di progettazione, di

modo che essi usino queste nuove risorse.

La suite di tool di progettazione Vivado è

stata aggiornata di conseguenza.

3) È stato necessario gestire una distor-

sione maggiore dei segnali di clock. La

temporizzazionenegli FPGAera caratteriz-

zata da una struttura centrale per la distri-

buzione del segnale di clock, che si dirama

quindi dal centro geometrico dell’IC per

fornire i segnali di temporizzazione a tutta

la logica su chip.

Tale sorta di schema globale di tempo-

rizzazione non funziona negli FPGA di

classe ASIC come quelli presenti nelle

famiglie di dispositivi interamente pro-

grammabili Virtex UltraScale e Kintex

UltraScale. L’aumento delle densità

dei blocchi CLB e della velocità dei se-

gnali di clock non lo permettono. Di

conseguenza, i dispositivi UltraScale si

avvalgono di uno schema di temporiz-

zazione radicalmente migliorato, come

mostrato in figura 3R.

C

OME OTTENERE

FPGA

CON CARATTERISTICHE DI CLASSE

ASIC

Fig.3R–Unnuovoschemaditemporizzazione

radicalmente nuovo è in grado di posizionare

più nodi per la distribuzione del clock al centro

geometrico di più domini di temporizzazione

su chip

Fig. 1R – Nell’architettura UltraScale l’utilizzo dei

blocchi logici configurabili èmigliorato e i requisi-

ti sul percorso dei segnali sono ridotti

Fig. 2R – La linea blu evidenzia la crescita

esponenziale dei blocchi CLB con l’aumento

della densità dei transistor. La linea retta in

rosso indica la crescita più lenta, lineare, delle

interconnessioni fra un blocco CLB e un altro,

usando le risorse di instradamento dei segnali

di generazione precedente. Si noti che la linea

retta in rosso sta divergendo rapidamente

dalla curva blu