55

- ELETTRONICA OGGI 437 - GIUGNO 2014

DIGITAL

HYBRID MEMORY

questo stato esso carica un byte dalla FIFO e lo trasfe-

risce a un accumulatore per l’ulteriore elaborazione. È

altresì possibile realizzare un contatore sfruttando risor-

se hardware aggiuntive (PLD) per tener traccia di ogni

byte, in quanto ciascun

byte è gestito in maniera

differente. Poiché il byte a

deve essere moltiplicato

per 2 (check_msb(a<<1)),

lo stato decisionale (Deci-

sion State) lo trasferisce

allo stato Shift dove viene

fatto scorrere a sinistra di

1 bit. Il bit in uscita (so in

Fig. 7) determina se è o

meno necessaria l’opera-

zione di XOR con 0x1B. In

modo analogo il contatore

incrementa e la macchina

a stati opera su ciascun

byte come previsto dall’e-

quazione.

Quando il contatore rag-

giunge un valore pari a 5

tutti i byte sono stati ca-

ricati, la FIFO di ingresso

è vuota e i risultati pos-

sono essere caricati nella

FIFO di uscita. La CPU può caricare il byte mescolato

d9.5onna di RK(n-1). La quarta colonna, infine, è

generata da un’operazione di XOR byte per byte

della terza colonna RK(n) e della quarta colonna

di RK(n-1).

Le operazioni di Key Expansion e Round Key Addi-

tion richiedono una certa quantità di memoria per

immagazzinare le chiavi a 128 bit correnti e attuali,

oltre ai risultati intermedi (Fig. 9).

Inoltre sono necessarie operazioni di XOR a livello

di byte. Il DMA può essere utilizzato per caricare i

byte dall’S-box indicato dalla quarta co-

lonna della chiave a 128 bit immagazzi-

nata in precedenza nella memoria e per

fornire in ingresso un byte alla volta ai

blocchi UDB.

Con l’ausilio di una semplice macchina

a stati per il percorso dati il blocco UDB

può far scorrere verticalmente questa

colonna. L’uscita può essere letta dalla

CPU oppure dal DMA.

Questa colonna può essere resa dispo-

nibile in ingresso alla FIFO del percorso

dati unitamente alla prima colonna per un’opera-

zione XOR byte per byte.

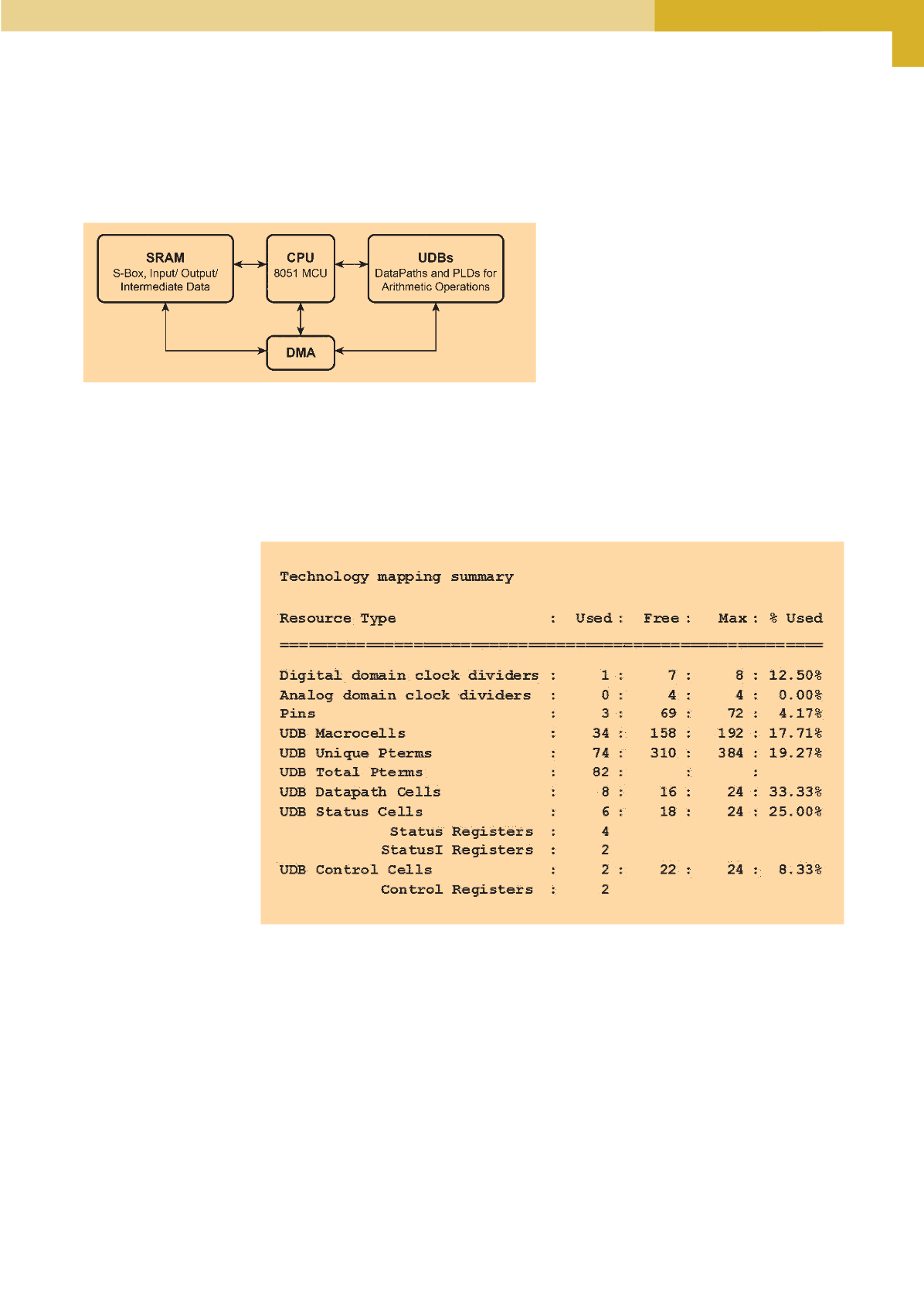

Nella figura 10 è riportato il consumo delle risor-

se di un progetto ottimizzato per il mescolamento

delle colonne descritto dalla macchina a stati di

figura 7. Sfruttando le risorse hardware aggiunti-

ve dei dispositive PSoC questo progetto utilizza un

numero di cicli macchina inferiore del 34% rispetto

a quello richiesto da una tradizionale implementa-

zione tramite CPU.

L’introduzione di interrupt contribuisce a ridurre ulte-

riormente il carico di lavoro della CPU.

Il trasferimento di tutti gli altri processi (in maniera totale

o parziale) a risorse hardware esterne permette un’imple-

mentazione più rapida ed efficiente dell’algoritmo AES.

Q

Fig. 10 – Consumo delle risorse di un progetto ottimizzato per il mescolamento delle colonne

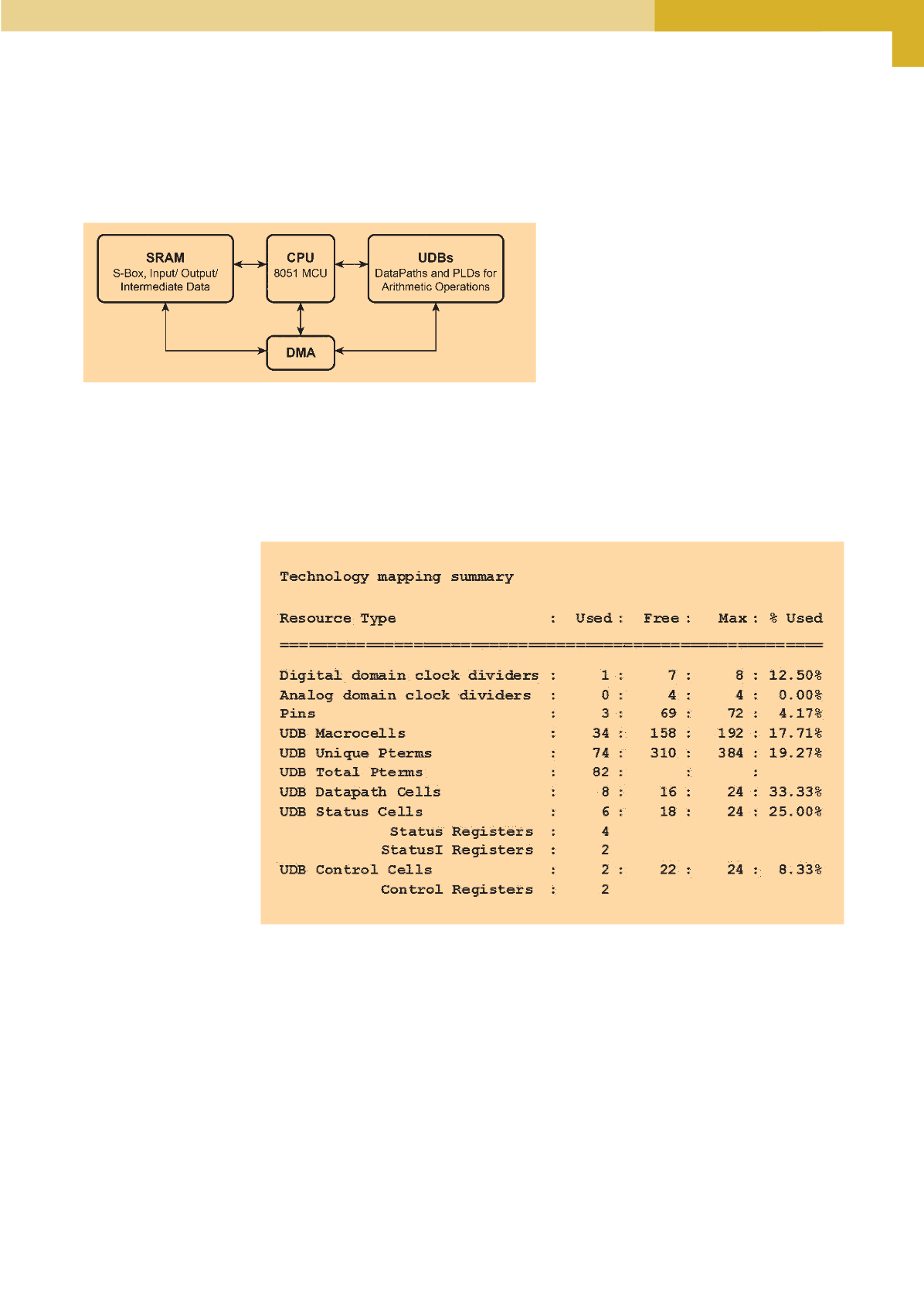

Fig. 9 – Integrazione dei blocchi digitali e del DMA nei dispositivi PSoC per la cifratura