49

- ELETTRONICA OGGI 434 - MARZO 2014

DIGITAL

DSP

secondo. Lo standard è stato

promosso per lo più da ARM

al momento dell’introduzione

della sua architettura Vector

Floating-Point (VFP) impiegata

nella famiglia dei core ARM 11.

Si tratta, tuttavia, di un’imposta-

zione di calcolo che richiede

registri generosamente ade-

guati a ricevere e reindirizzare

buone quantità di dati vettoriali

ed è perciò efficiente solo fin-

ché i vettori non sono troppo

grandi (sugli ARM 11 bastava

all’incirca una decina di ope-

randi contemporanei in singola

precisione o la metà in doppia

precisione). Oltre si rischia di

rallentare la velocità di calcolo

del processore e perciò frenare

i flussi di dati che scorrono in

parallelo senza ottenere alcun

vantaggio dal maggior costo

delle infrastrutture circuitali

necessarie.

Va considerato che oltre a

richiedere più tempo i calcoli

in virgola mobile necessitano

di dati larghi come minimo 32

o 64 bit mentre per i dati inte-

ri bastano 8 o 16 bit e perciò

con la virgola fissa diminui-

scono di conseguenza anche

le dimensioni della memoria, i

consumi di potenza e la dissipa-

zione termica dovuta al minor

assorbimento di corrente. Ciò

significa che il calcolo vettoriale in virgola mobile richiede

risorse sul silicio più ingombranti rispetto al corrispettivo in

virgola fissa e perciò necessita di supporti adeguati come

PC desktop, consolle di gioco o set-top box multimediali,

mentre sugli apparecchi portatili di ultima generazione

come smartphone e tablet dove la durata della batteria è

pur sempre un parametro critico ci si può accontentare

della virgola fissa. Senza dubbio questo può essere un cri-

terio di scelta preferibile per i progettisti di prodotti palmari,

tenendo conto che oggi si può anche realizzare in hardware

un’architettura DSP in virgola fissa e poi implementare degli

algoritmi di calcolo in virgola mobile via software che forse

possono rallentare un po’ la velocità operativa complessiva,

ma consentono di ottenere ugualmente una soddisfacente

precisione algebrica.

Core ARM

ARM ha sviluppato la sua originale architettura Vector

Floating-Point VFP creando progressivamente la VFPv1

oggi obsoleta, la VFPv2 tuttora utilizzata nei core ARMv5

e ARMv6, la versione VFPv3 che anima i core ARMv7 e

l’ultima VFPv4 ideale per i nuovi core ARMv8 a elevate

prestazioni e basso consumo. Le prestazioni matematiche

garantite sui VFPv2 sono di 2,0 Mflops/MHz, 4,01 DMIPS/

MHz e meno di 0,4 mW/MHz con un’occupazione sul silicio

di 1,16 mm

2

in tecnologia Tsmc da 0,13 μm. I più recenti

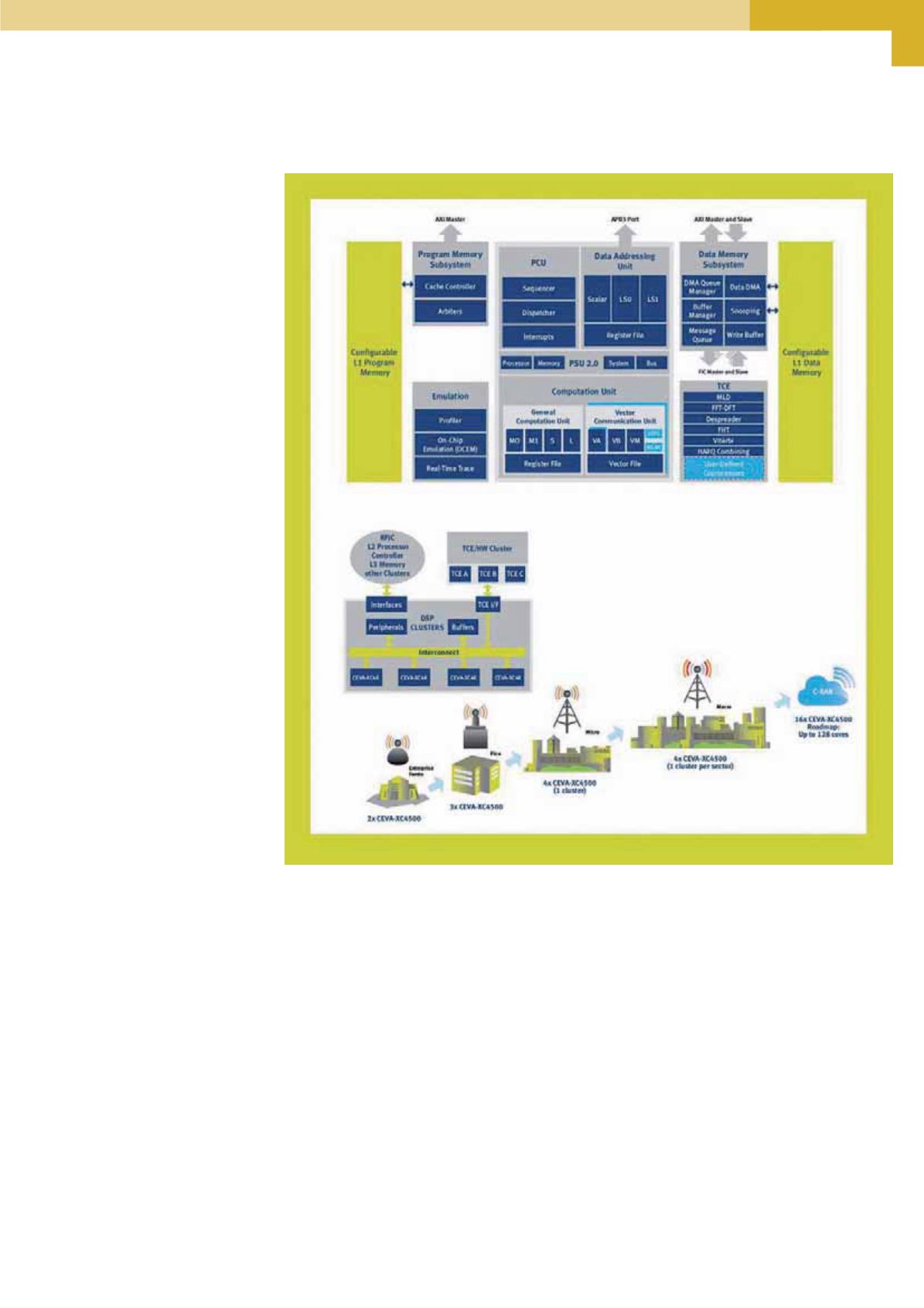

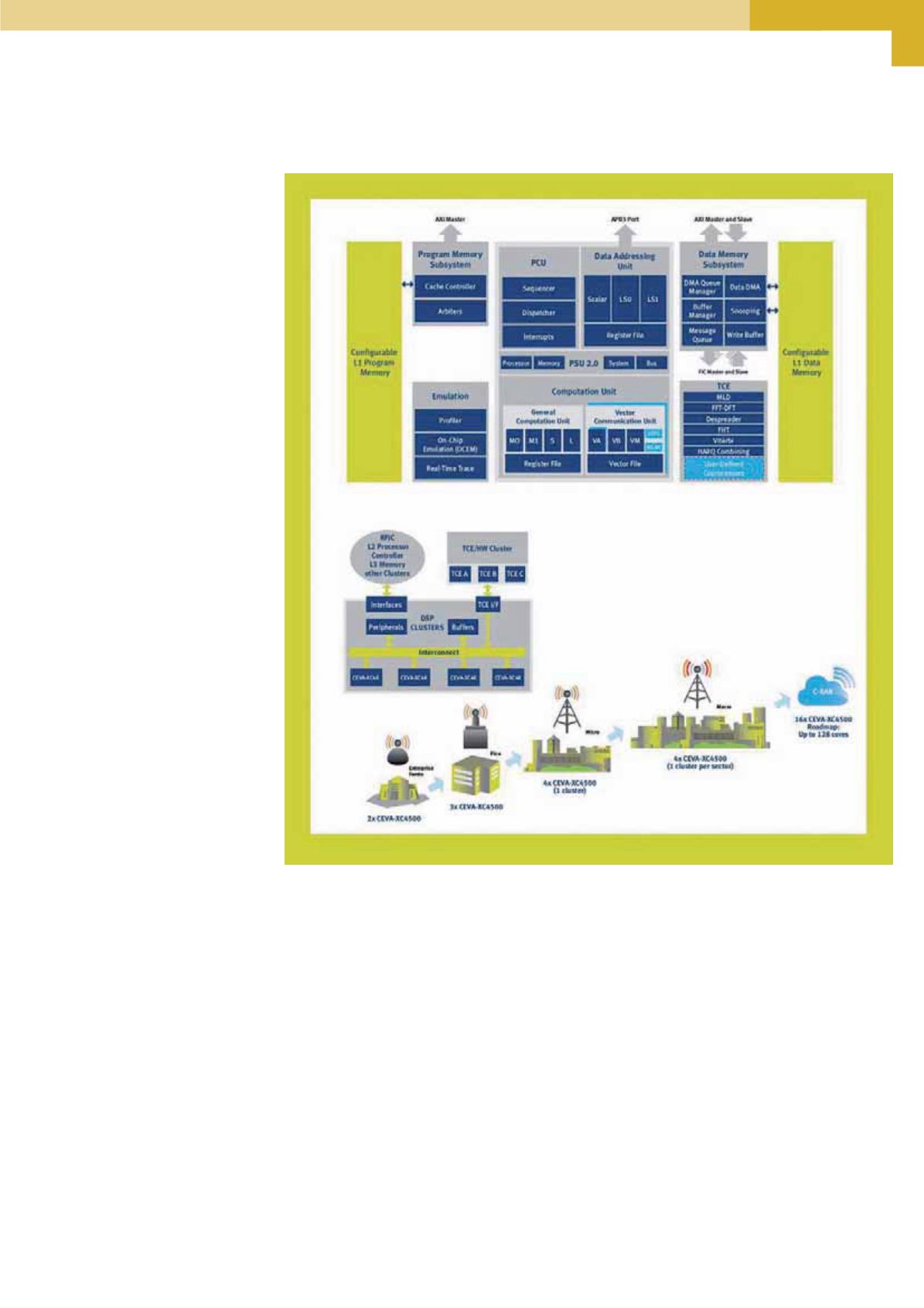

Fig. 2 – I nuovi processori DSP CEVA-XC4500 con potenza di calcolo vettoriale di 40 Gflops permettono di realizzare le

piccole e medie celle delle infrastrutture wireless di nuova generazione