22

- ELETTRONICA OGGI 434 - MARZO 2014

COVERSTORY

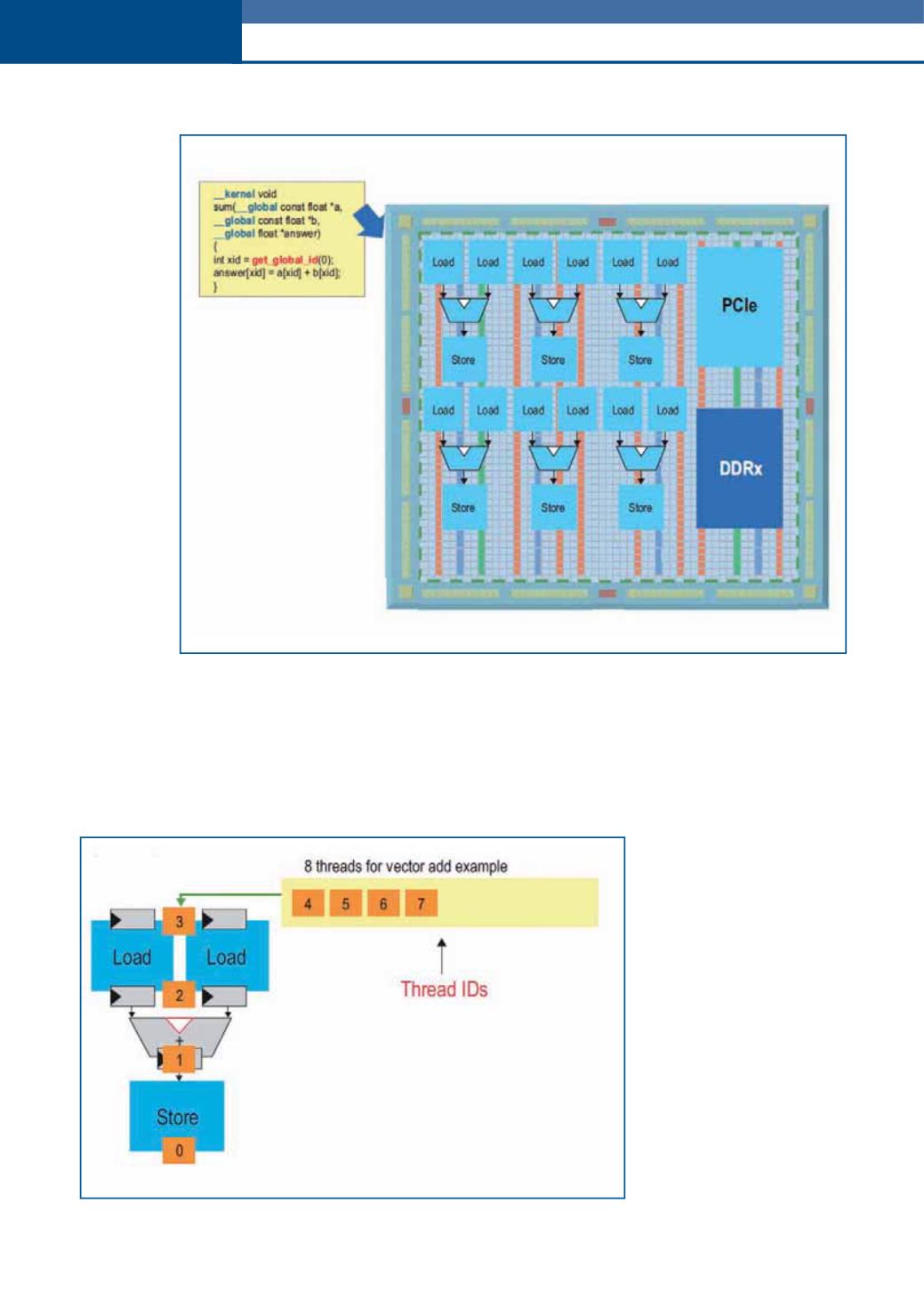

in precedenza, relativo alla somma vettoriale, la

conversione in hardware darà luogo a una sem-

plice pipeline feed-forward. Le istruzioni di cari-

camento (load) degli array A e B sono convertiti

in unità di caricamento (load unit), piccoli circuiti

il cui compito è inviare gli indirizzi alla memoria

esterna ed elaborare i dati restituiti. I due valori

resi vengono inviati direttamente a un addiziona-

tore che effettua l’addizione in virgola mobile di

questi due valori. Il risultato dell’addizione è col-

legato direttamente a un’unita di memorizzazione

(store unit) che si occupa della scrittura nella me-

moria esterna.

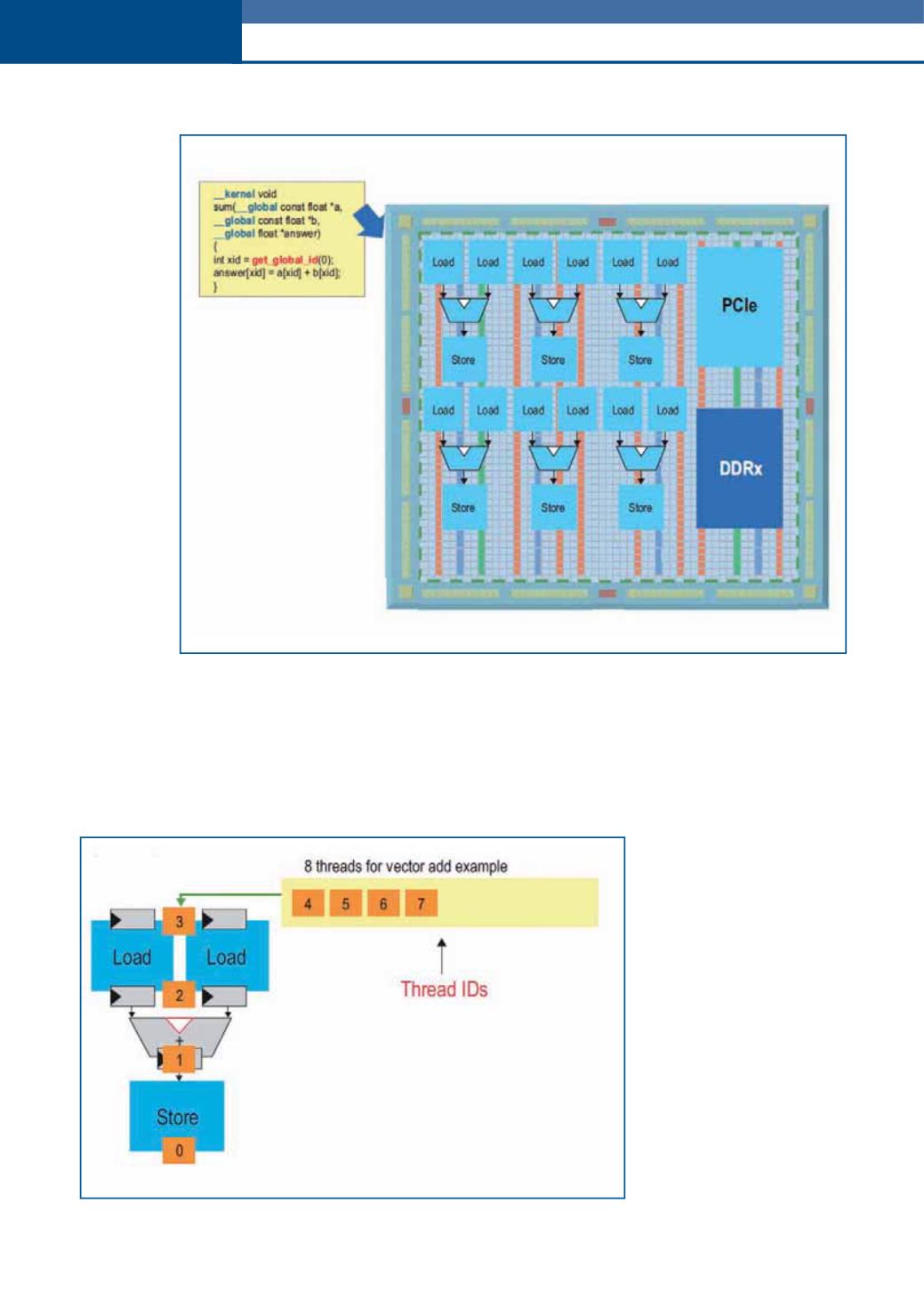

Il concetto più importante alla base del compila-

tore OpenCL-FPGA è la nozione di parallelismo

della pipeline. Per semplicità si faccia l’ipotesi

che il compilatore abbia crea-

to tre stadi della pipeline per il

kernel, come riportato in figura

3. In corrispondenza del primo

ciclo di clock, il thread 0 è tem-

porizzato in due unità di carica-

mento. Ciò significa che esse

possono iniziare il fetching (ov-

vero il prelievo) dei primi ele-

menti di dati dagli array A e B.

In corrispondenza del secondo

ciclo di clock, il thread 1 è tem-

porizzato nello stesso momento

in cui il thread 0 ha completa-

to la sua lettura dalla memoria

e immagazzinato i risultati nei

registri che seguono le unità

di caricamento. In corrispon-

denza del terzo ciclo di clock,

il thread 2 è temporizzato, il

Fig. 2 – Esempio di

implementazione di

OpenCL su un FPGA

Fig. 3 – Il concetto alla base del

compilatore OpenCL-FPGA è il

parallelismo della pipeline