21

- ELETTRONICA OGGI 434 - MARZO 2014

re (HDL – Hardware Description Language) come

VHDL o Verilog. Nonostante siano reperibili nu-

merosi tool per la sintesi ad alto livello in grado

di sfruttare i vantaggi derivati da questo elevato

livello di astrazione, tutti si trovano ad affrontare

il medesimo problema. Essi operano su program-

mi sequenziali scritti in C e producono un’imple-

mentazione HDL parallela. La difficoltà non risie-

de tanto nella generazione dell’implementazione

HDL, bensì nell’estrazione del parallelismo a li-

vello di thread che consente all’implementazione

FPGA di garantire elevate prestazioni. Poiché gli

FPGA sono dispositivi caratterizzati da un eleva-

to grado di parallelismo, il mancato ottenimento

del massimo livello possibile di parallelismo è

più penalizzante rispetto ad altri dispositivi. Lo

standard OpenCL permette di risolvere molti di

questi problemi consentendo al programmatore

di specificare in maniera esplicita e controllare il

parallelismo.

Lo standard OpenCL risulta quindi più adatto

alla natura parallela intrinseca degli FPGA ri-

spetto a quanto lo siano i programmi sequen-

ziali scritti in C.

Una breve descrizione dello standard OpenCL

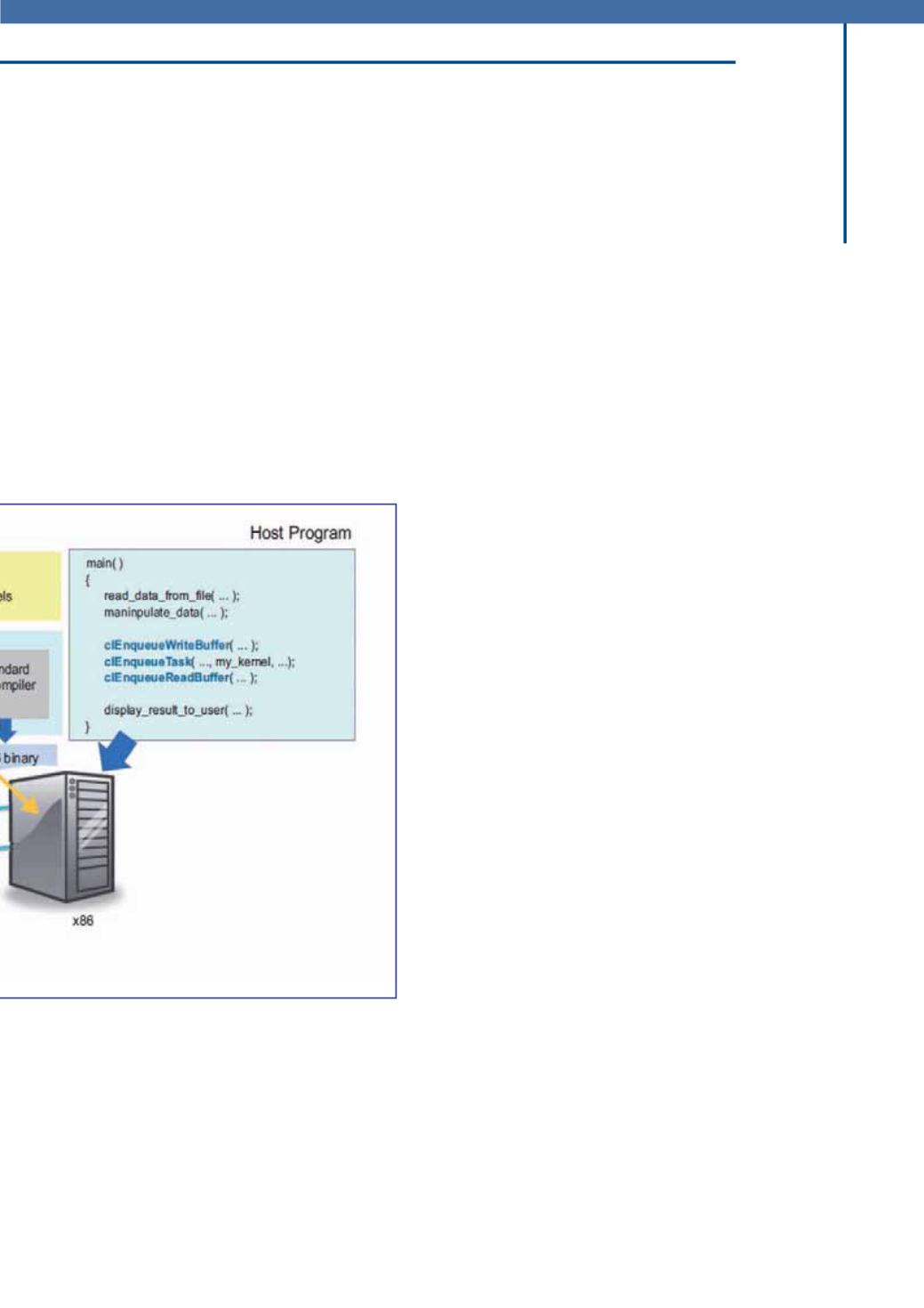

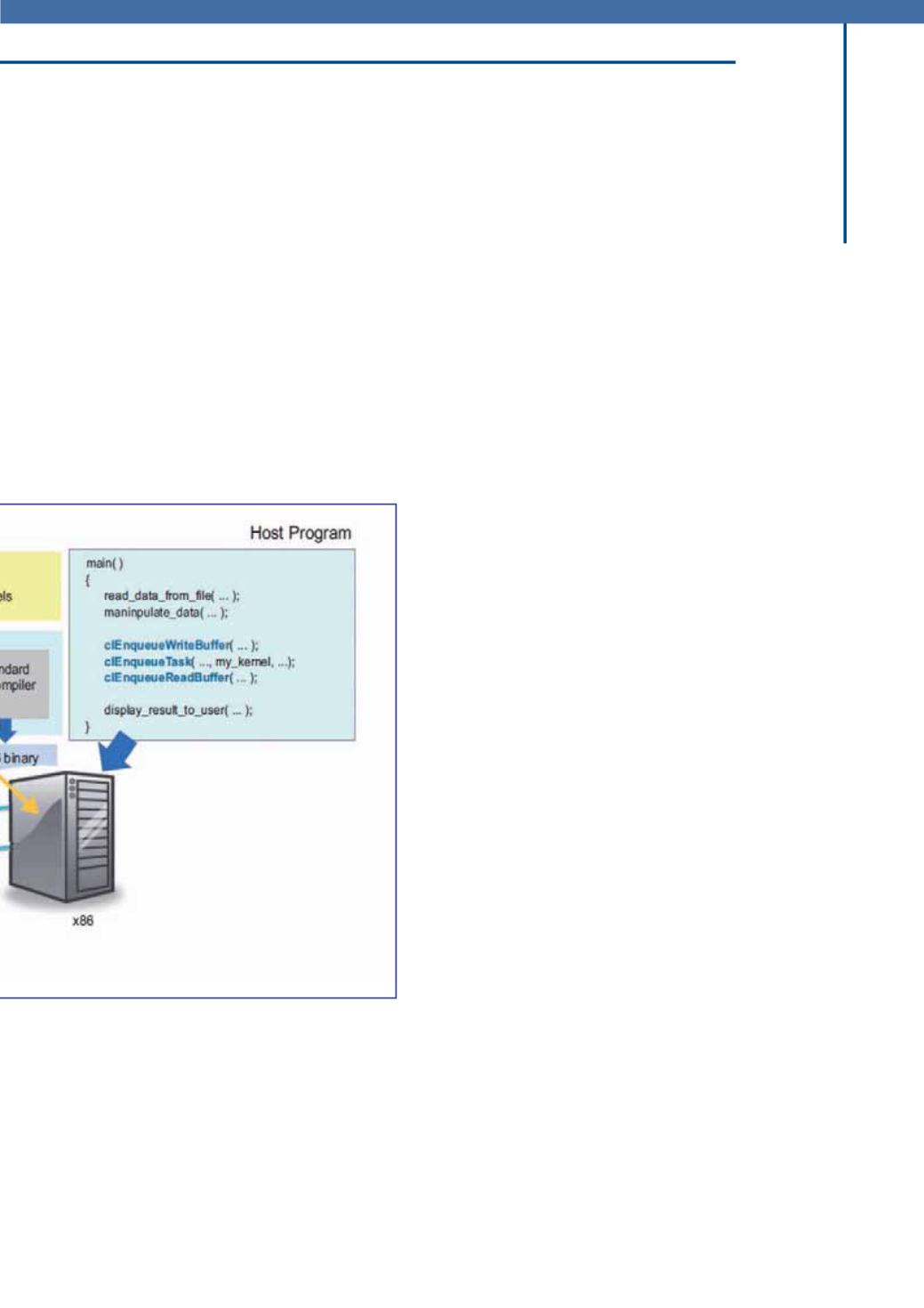

Le applicazioni OpenCL risultano composte da

due parti. Il programma host OpenCL è una routi-

ne software scritta in linguaggio standard C/C++

che gira su qualsiasi tipo di microprocessore.

Questo può essere un processore soft integrato

in un FPGA, un processore ARM di tipo hard o

un processore in architettura x86 esterno, come

visibile in figura 1.

Durante l’esecuzione nell’host di questa routine

software, a un certo punto è possibile che vi sia

una funzione, particolarmente onerosa in termi-

ni computazionali, che possa trarre vantaggio

dall’accelerazione parallela se eseguita su un di-

spositivo ad alto grado di parallelismo come ad

esempio CPU, GPU, FPGA e così via. La funzione

che deve essere accelerata viene definita kernel

OpenCL. Tali kernel, sebbene scritti in linguaggio

C standard, sono annotati con costrutti che spe-

cificano il parallelismo e la gerarchia di memoria.

L’esempio riportato in figura 2 esegue la somma

vettoriale di due array, A e B, e scrive i risulta-

ti in un array di uscita. I thread (ovvero i flussi

di esecuzione) paralleli che operano su ciascun

elemento del vettore consentono di calcolare il

risultato in tempi notevolmente più brevi quando

si sfrutta l’accelerazione tipica di un dispositivo

caratterizzato da un massiccio parallelismo a

grana fine come appunto un FPGA. Il programma

host ha accesso alle API (Application Program-

ming Interface) OpenCL standard che consento-

no il trasferimento dei dati all’FPGA mediante la

chiamata del kernel sull’FPGA e il trasferimento

dei dati risultanti.

A differenza di CPU e GPU, dove i thread paral-

leli possono essere eseguiti su differenti core,

per gli FPGA si adotta una strategia differente.

Le funzioni del kernel possono essere trasforma-

te in circuiti hardware dedicati e di tipo deeply

pipelined (pipeline profonda) che sono intrin-

secamente multithreaded grazie all’utilizzo del

concetto di parallelismo della pipeline (pipeline

parallelism). Ciascuna di queste pipeline può es-

sere replicata molte volte al fine di ottenere un

grado di parallelismo più spinto rispetto a quello

conseguibile con una singola pipeline. Il compi-

latore OpenCL di Altera, ad esempio, converte

un kernel OpenCL in hardware dando vita a un

circuito che implementa ciascuna operazione.

Questi circuiti sono collegati insieme per imitare

il flusso di dati nel kernel. Nell’esempio riportato

ALTERA

Fig. 1 – Una panoramica di OpenCL,

lo standard aperto per la program-

mazione parallela