EMBEDDED

51 • FEBBRAIO • 2014

56

HARDWARE

DIGITAL POWER

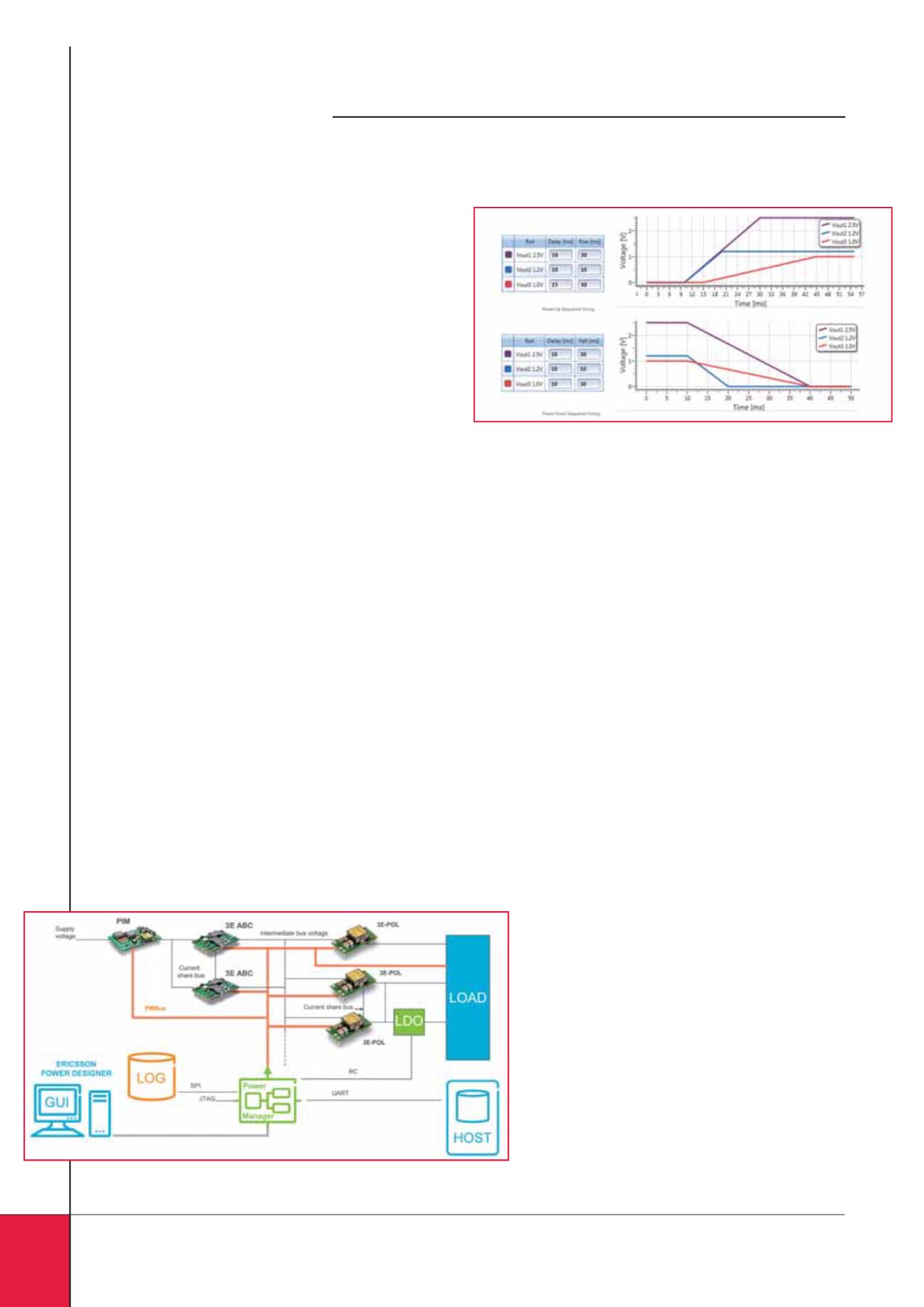

to, in un intervallo di 10 ms; il tempo di discesa, in ogni caso, è

regolato in modo da assicurare una transizione uniforme fino al

momento in cui tutte le funzioni sono disattivate.

Come menzionato in precedenza, durante la fase di progettazio-

ne dell’apparecchiatura i parametri evolvono in modo continuo

e, nel caso in cui varino i requisiti di messa in sequenza, i pro-

gettisti del sistema di alimentazione possono semplicemente

modificare il valore e inviare nel giro di pochi minuti un set di

comandi da caricare nel regolatore POL oppure un nuovo file di

configurazione per il BPM (Board Power Manager). Le mede-

sime operazioni possono essere effettuate quando il sistema è

in funzione ed è necessario un aggiornamento del firmware che

prevede una differente messa in sequenza delle tensioni al fine

di ottimizzare le prestazioni.

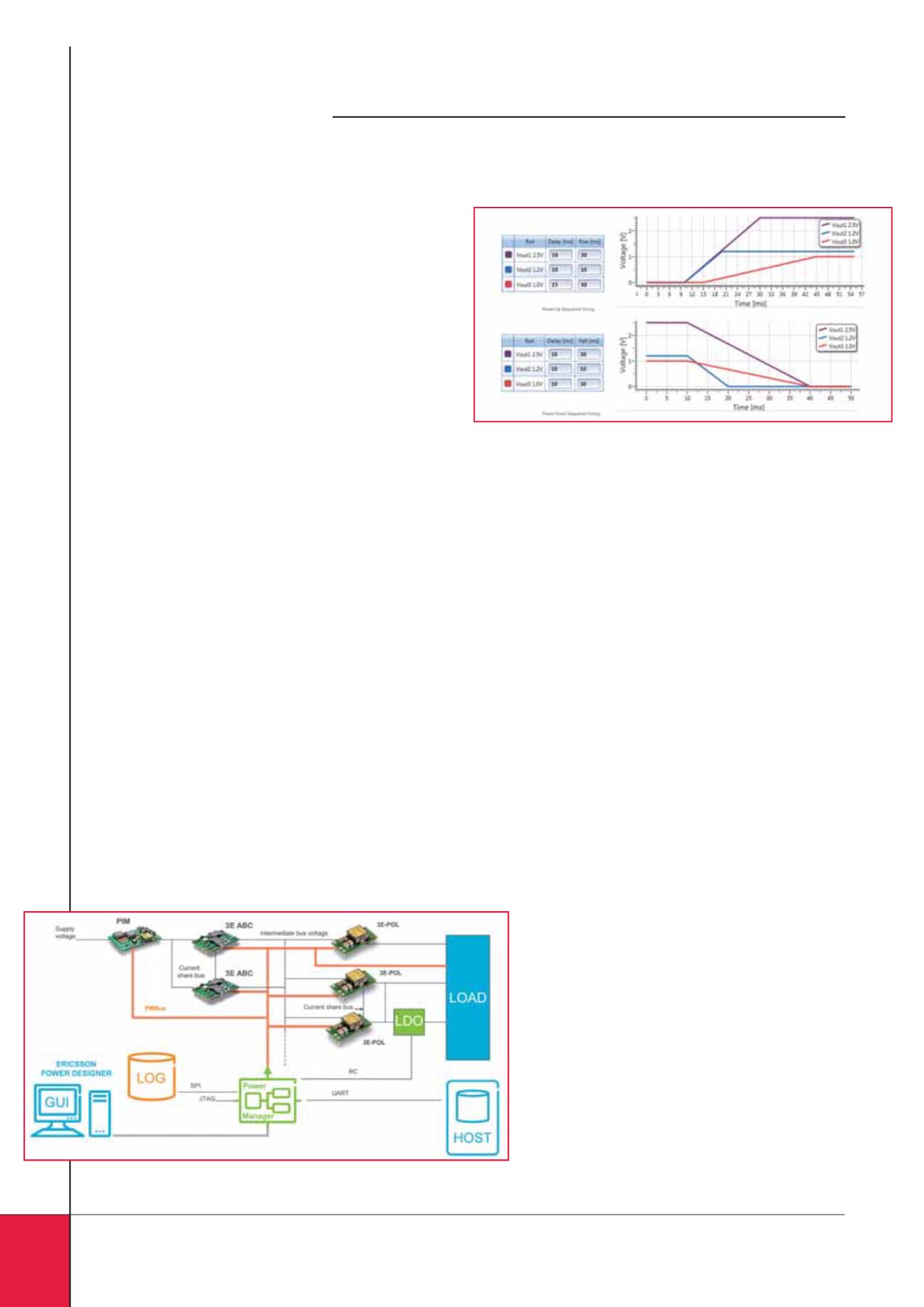

Come si può dedurre osservando lo schema di figura 5, i sistemi

che utilizzano un’architettura di alimentazione digitale risultano

estremamente flessibili e il responsabile del sito può accedere a

qualsiasi sezione della scheda, fino ad arrivare al singolo regola-

tore POL, attraverso l’interfaccia digitale.

Alimentare il core risparmiando energia

Nel corso degli anni l’industria dei semiconduttori ha compiuto

notevoli progressi nel campo dell’ottimizzazione dell’utilizzo

dell’energia grazie all’integrazione di funzioni di gestione

dell’energia all’interno del processore che hanno contribuito

a migliorare significativamente le prestazioni e a ridurre i

consumi. Gli odierni smartphone, tablet e laptop sono tutti

dispositivi che hanno tratto notevoli benefici da questa evo-

luzione. I processori di fascia alta usati nelle apparecchiature

per reti di trasmissione dati sono caratterizzati da una potenza

di elaborazione sempre più spinta, raggiungendo throughput

anche superiori a 300 Mbps, mentre il numero dei core presenti

nei singoli processori sta superando i limiti dettati dalla legge

di Moore. Un maggior numero di core e l’incremento della

potenza richiedono l’adozione di tecnologie di processo caratte-

rizzate da geometrie sempre più ridotte che richiedono tensioni

inferiori e correnti più elevate.

La tensione dei core è attualmente dell’ordine del Volt (e anche

inferiore) mentre la corrente, che può arrivare a 90A per un

processore operante al massimo delle sue prestazioni, si riduce

drasticamente (10A o anche meno) in caso di scarso utilizzo.

Per alimentare in maniera efficiente il processore, i progettisti

possono sfruttare un altro vantaggio tipico del controllo digitale

dell’alimentazione, ovvero quello di poter collegare un certo

numero di regolatori POL in parallelo. Per esempio è possibile

utilizzare 3 regolatori POL in parallelo per garantire una cor-

rente di 100A in tutte le condizioni e sfruttare i vantaggi legati

all’uso delle tecniche di “phase spreading” (dispersione di fase)

per diminuire i fenomeni di ondulazione e rumore alla massima

potenza e di “phase shading” (schermatura di fase) per ridurre,

in base alle condizioni operative, il numero di regolatori POL in

funzione. Sebbene complessa da gestire, l’implementazione di

questo tipo di funzionalità con i regolatori POL di tipo digitale

risulta alquanto semplice.

Nella figura 6 viene riportato un esempio di regolazione delle

fasi effettuato mediante Ericsson Power Designer. Come acca-

de per la messa in sequenza, anche le operazioni di “

phase spreading” e di “phase shading” possono essere

programmate in maniera molto semplice. Coloro che si

occupano dell’architettura del sistema possono svilup-

pare più file di configurazione per soddisfare le esigen-

ze di determinati profili che possono essere richiamati

dal BPM (Board Power Management) dalla memoria

locale. In alcune applicazioni il processore comunica

direttamente con il BPM per impostare il numero di

fasi richieste, per ottenere prestazioni ottimizzate e le

modalità da seguire per sincronizzare o variare queste

fasi.

Questo semplice esempio dà un’idea delle potenzialità

offerte dai regolatori POL di tipo digitale in grado di

comunicare direttamente con il processore principale

(master).

Fig. 4 – Esempio di messa in sequenza time-based

– tempi di salita e di discesa

Fig. 5 – Schema di un sistema che utilizza un’architettura

di alimentazione digitale