LIGHTING 7 - gennaio/febbraio 2015

IX

LED BIANCHI

durezza, alto punto di fusione e grande resistenza alla

rottura e all’erosione per poter sopportare i processi di

fabbricazione degli stessi LED. I chip LED ancora grez-

zi emettono una luce a lunghezze d’onda che ricadono

prevalentemente nello spettro blu e che vengono con-

vertite applicando sul chip uno strato di fosforo apposi-

tamente studiato e realizzato per emettere luce bianca

alla temperatura di colore desiderata. Quest’ultima può

ricadere nell’intervallo fra 4000 °K e 6000 °K per i LED

a luce bianca fredda, impiegati nell’industria o per l’illu-

minazione stradale, oppure nell’intervallo compreso fra

2700 °K e 3500 °K per il bianco caldo tipicamente usato

nell’illuminazione di ambienti residenziali.

In base poi alla tecnologia di confezionamento (packa-

ge), il sottile strato (die) ricoperto di fosforo può essere

fissato ad un substrato termicamente efficiente e ad

una struttura metallica conduttrice (leadframe) che

fornisce le connessioni di anodo e catodo; infine,

vengono applicati un riflettore ed una lente ottica-

mente trasparente in policarbonato. In alternativa,

il die può essere fissato all’interno della cavità del

riflettore di un contenitore (package) plastico con

piedini a forma di “J” (tipo “PLCC”: Plastic Leaded

Chip Carrier) e incapsulato con resina epossidica o

silicone.

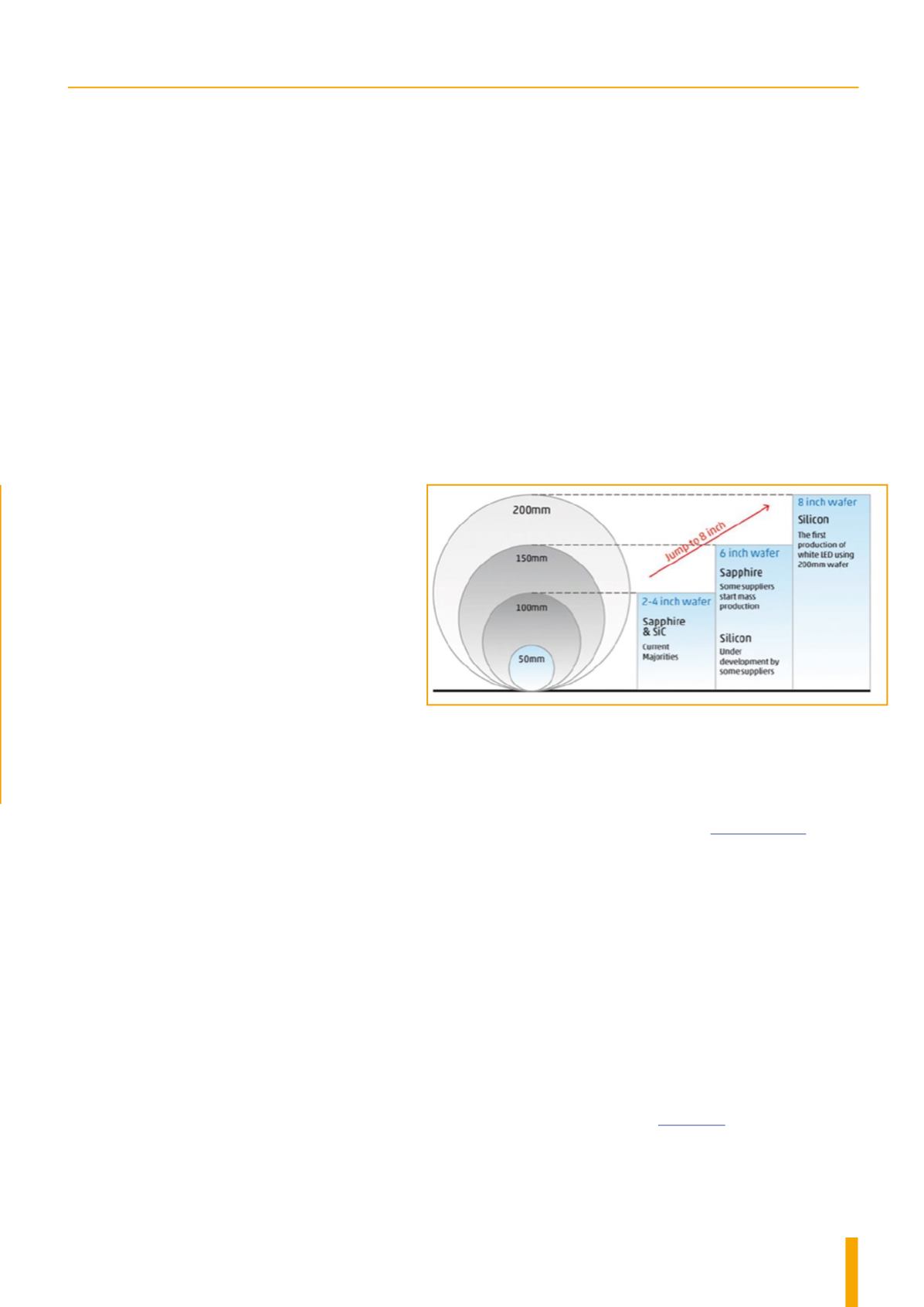

Una sottile fetta (wafer) di zaffiro è stata storicamen-

te scelta quale substrato per la fabbricazione dei die

per i LED. La produzione di LED costituiti da GaN

su zaffiro richiedeva tipicamente wafer con diametri

di 2 o 4 pollici. Più recentemente, invece, il supe-

ramento di alcuni ostacoli tecnici ha consentito di

produrre wafer di zaffiro con diametri che arrivano

a 6 pollici, mantenendo una qualità sufficiente a garan-

tire un’adeguata resa di dispositivi LED. Maggiore è la

dimensione del wafer, infatti, più alto è il numero otteni-

bile di die per wafer, portando così a economie di scala;

più efficiente risulta, inoltre, lo sfruttamento dell’area

del wafer medesimo, con una conseguente riduzione de-

gli effetti di perdita ai bordi e di spazio inutilizzato fra i

singoli die. Tuttavia, altri fattori, come il costo delle nuo-

ve apparecchiature per processi quali l’attacco corrosivo

(etching) e il test dei wafer da 6 pollici, possono impe-

dire ai produttori di ottenere rapide riduzioni dei costi.

Tecnologie del substrato per abbattere i costi

Sono state sviluppate parecchie tecnologie alternati-

ve per il substrato, allo scopo di migliorarne le diverse

caratteristiche. Ad esempio, il GaN-su-GaN e il GaN-su-

carburo di silicio (GaN-su-SiC) presentano una disuni-

formità nulla, o comunque molto bassa, fra il materiale

dello stesso substrato e la struttura attiva del LED, pro-

prietà, questa, che ne accresce l’efficienza. L’impiego di

wafer di silicio puro, d’altra parte, può generare risparmi

significativi, non solamente per il fatto che il silicio co-

sta solamente un ottavo del substrato in zaffiro (secondo

le cifre riportate da Lux Research), ma anche perché i

produttori avrebbero la possibilità di utilizzare apparec-

chi e processi di fabbricazione dei semiconduttori ormai

ben consolidati per wafer che arrivano a un diametro di

8 pollici (200 mm). Wafer di silicio da 8 pollici, infatti,

sono già disponibili e, allo stesso modo, sono già ben

definite anche le relative tecnologie di processo, ormai

collaudate ed economicamente vantaggiose.

La figura 2 sintetizza l’attuale situazione della produzio-

ne di LED in GaN su wafer di zaffiro e di silicio nelle

diverse dimensioni.

Le principali società di ricerca hanno pubblicato diverse

previsioni che preannunciavano i probabili effetti del-

la tecnologia GaN su silicio per realizzare i LED. Nel

dicembre del 2013, ad esempio,

IMS Researchriscon-

trò che, per i wafer di GaN su Silicio, il mercato sareb-

be aumentato a un tasso di crescita annuale composto

(CAGR) del 69% per arrivare a conquistare una quota

di penetrazione superiore al 40% entro il 2020. IMS con-

frontò la difficoltà nel produrre grandi lingotti di zaffiro

con l’abbondante disponibilità di wafer di silicio a basso

costo con diametro da 200 mm o anche superiore; nella

suddetta ricerca, IMS menzionò, inoltre, la possibilità di

impiegare apparecchiature e processi che erano già in

grado di trattare wafer di silicio da 200 e più millimetri,

come importanti fattori che avrebbero spinto la crescita

della quota di mercato del GaN su Silicio.

Piani di sviluppo del GaN su Silicio

Toshiba ha lavorato con

Bridgelux, ditta specializzata

nella tecnologia dell’illuminazione, per implementare

un apposito processo adatto a fabbricare LED in GaN

su wafer di silicio da 200 mm, che combinasse l’avanzato

processo di lavorazione del silicio messo a punto da To-

Fig. 2 – Dimensioni maggiori del wafer consentono un

minor costo per die, ma risultano più difficili da produrre

in zaffiro