ANALOG/MIXED SIGNAL

TIMING

28

- ELETTRONICA OGGI 440 - OTTOBRE 2014

del sistema. Ciò non solo permette di ridurre costi e ingom-

bri sulla scheda, ma semplifica anche il progetto in termini

dei requisiti di compatibilità elettromagnetica (EMC) grazie

all’eliminazione di diversi generatori ad alta frequenza. In

aggiunta, un pin del chip VersaClock fornisce una versio-

ne “bufferizzata” del generatore di riferimento, il che evita in

molte applicazioni il ricorso a un secondo cristallo.

Oltre a ridurre costi e numero di componenti, l’utilizzo di un

temporizzatore integrato multicanale può anche contribuire

a diminuire notevolmente i rischi di approvvigionamento,

dal momento che gli acquirenti devono gestire la disponibi-

lità di un solo componente al cristallo per garantire la conti-

nuità della produzione.

I progettisti possono risparmiare spazio su scheda e ottenere

consumi più bassi utilizzando un unico dispositivo integrato

per generare più riferimenti di clock, anziché ricorrere a più

componenti discreti. La serie VersaClock 5 adotta tecniche

di progettazione a bassa potenza per ridurre il consumo di

energia del core, che risultano inferiori a 100 mW (oppure

minori di 300 mW con tutte le uscite operative). Si tratta di

valori di assorbimento molto inferiori rispetto a quelli di ana-

loghi circuiti di clock multicanale presenti sul mercato. La

riduzione complessiva della potenza del sistema semplifica

il progetto dell’alimentatore, “allenta” i vincoli di natura ter-

mica e ottimizza la durata della batteria.

Minimizzare il valore

efficace del jitter

Le prestazioni del jitter dei generatori integrati di clock pro-

grammabili è andato progressivamente migliorando nel cor-

so del tempo per soddisfare i vincoli imposti dagli standard

di connettività ad alta velocità. I di-

spositivi VersaClock 5 sono caratte-

rizzati da un valore efficace del jitter

di fase inferiore a 0,7 picosecondi

sull’intero intervallo di integrazione

da 12 kHz a 20 MHz.

Standard di interconnessione ad alta

velocità come Ethernet 1G o Ethernet

10G e PCI Express Gen 3 specificano

un jitter massimo che tiene conto dei

contributi di tutte le sorgenti di jit-

ter. Queste comprendono non solo il

clock, ma anche il trasmettitore, non-

ché le terminazioni e le piste del cir-

cuito stampato. Il valore efficace del

jitter consentito in una connessione

Ethernet 10G può essere di soli 1,55

ps (10G BASE-R), mentre PCI Express

Gen 3 specifica un valore efficace di

jitter pari a 3,0 ps per il collegamento.

La minimizzazione del valore efficace del jitter di fase prodot-

to dal generatore di clock assicura al progettista un margine

più ampio per rispettare i limiti ammissibili per il jitter del

collegamento quando si tengono in considerazione anche al-

tri contributi. Con un valore efficace di jitter di fase inferiore

a 0,7 ps, la tecnologia VersaClock garantisce un margine più

ampio per il jitter in presenza di queste connessioni o, più in

generale, di connessioni ad alta velocità come SONET, Fibre

Channel e XAUI.

Configurazione e programmazione

in-system

Alcune applicazioni possono richiedere una rete di distribu-

zione del clock integrata che può essere collegata in-circuit

e si attiva direttamente nella configurazione desiderata. Ver-

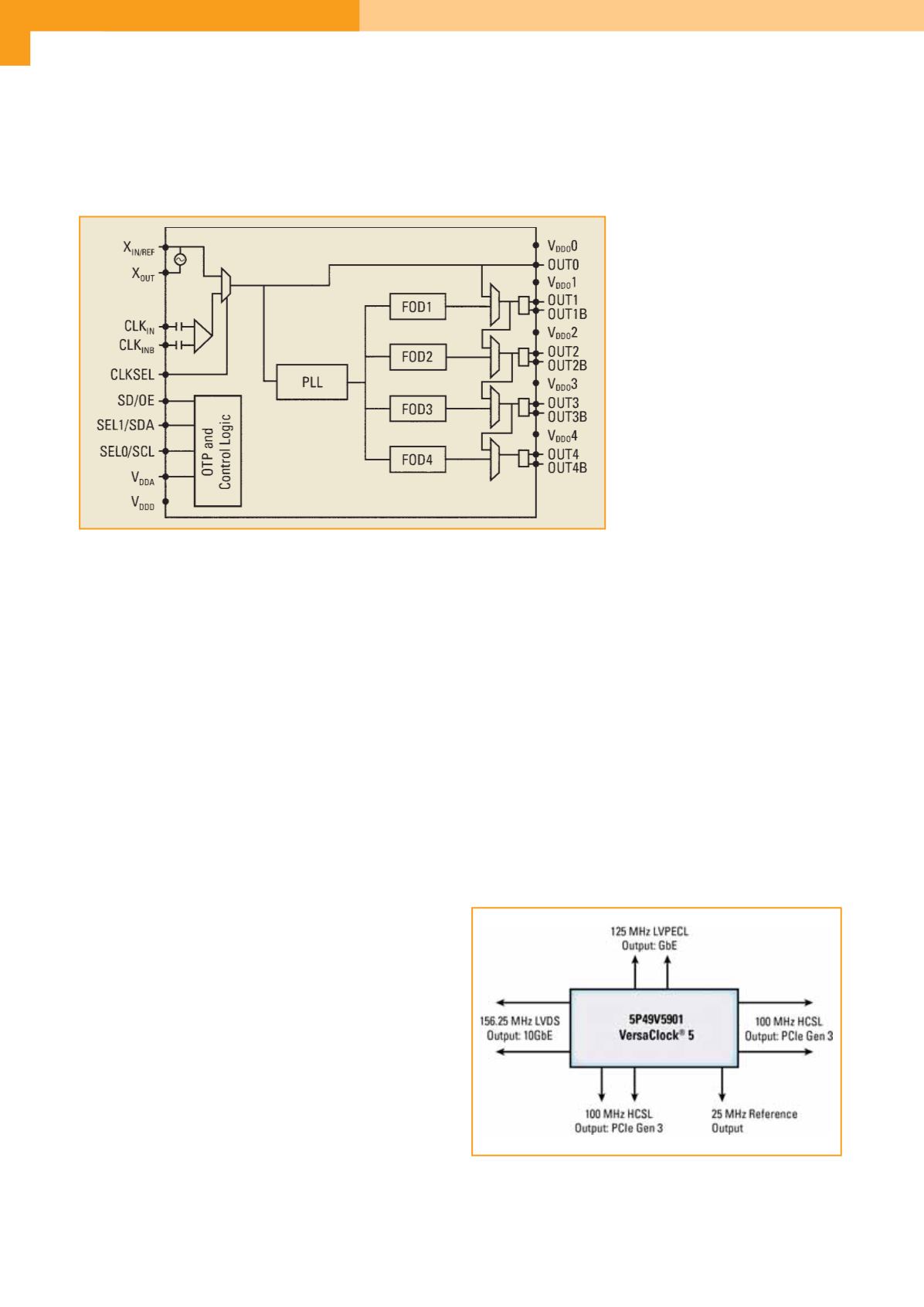

Fig. 1 – I divisori di uscita frazionari programmabili generano più uscite di clock a partire da un unico

ingresso di riferimento

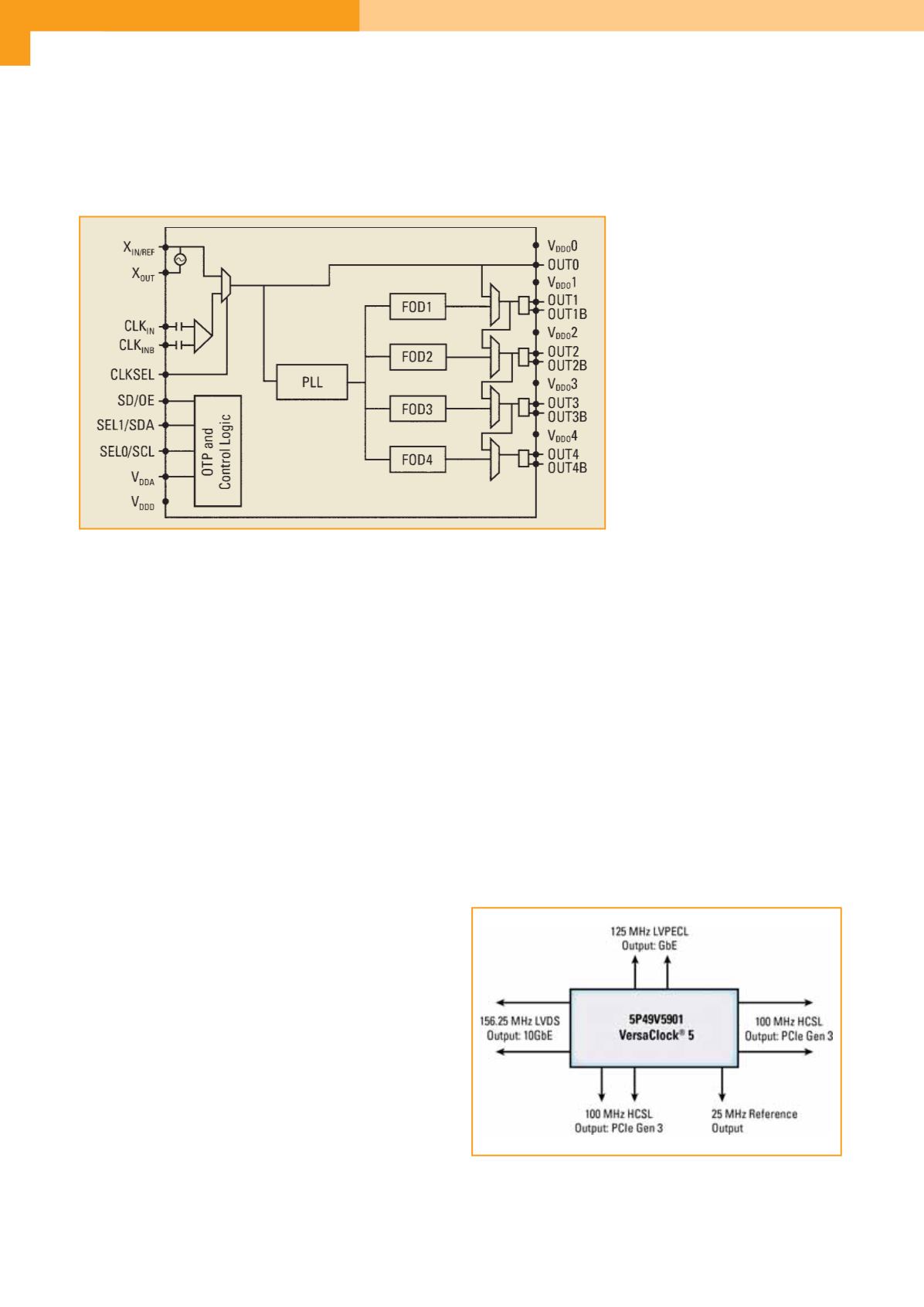

Fig. 2 – Un singolo circuito di clock può generare riferimenti di tempo-

rizzazione per più interconnessioni di dati ad alta velocità